ผลิตภัณฑ์

19

Jan

เครือข่ายบนชิป (Network-on-Chip หรือ NoC): การเชื่อมต่อสำหรับ SoC แบบมัลติคอร์

เรียนรู้ว่า Network-on-Chip (NoC) มอบโครงสร้างพื้นฐานความเร็วสูงสำหรับโปรเซสเซอร์มัลติคอร์สมัยใหม่ได้อย่างไร

การศึกษาค้นคว้าประสิทธิภาพการคำนวณและการประหยัดพลังงานได้ส่งเสริม อุตสาหกรรมเซมิคอนดักเตอร์ไปสู่ระบบบนชิป (System-on-Chip หรือ SoC) ซึ่งรวม เอาแกนประมวลผล ตัวเร่งความเร็ว และระบบหน่วยความจำย่อย จำนวนหลายสิบถึง หลายร้อยตัวเข้าไว้ด้วยกัน การเปลี่ยนแปลงทางสถาปัตยกรรมนี้ทำให้การเชื่อมต่อแบบบัสร่วม และครอสบาร์แบบดั้งเดิมล้าสมัย เนื่องจากมีข้อจำกัดด้านความสามารถในการขยาย หรือ เพิ่มขนาด ปัญหาคอขวดด้านแบนด์วิดท์ และความหน่วงแฝงที่เพิ่มขึ้นทุกครั้งที่มีการเพิ่มส่วนประกอบ

ความท้าทายนี้ จึงกลายเป็นการพยายามค้นหาหนทางอำนวยความสะดวกในการ สื่อสารระหว่างบล็อกทรัพย์สินทางปัญญา (IP) จำนวนมากบนชิปให้ได้ประสิทธิภาพ และมีประสิทธิภาพ ทางออกนี้จึงเกิดขึ้นจากการปรับใช้แนวคิดเครือข่ายขนาดใหญ่ ที่รู้จักกันดีในระดับไมโคร จนทำให้เกิดแนวคิดเครือข่ายบนชิป (Network-on-Chip หรือ NoC) ขึ้น

การกำหนดสถาปัตยกรรม NoC

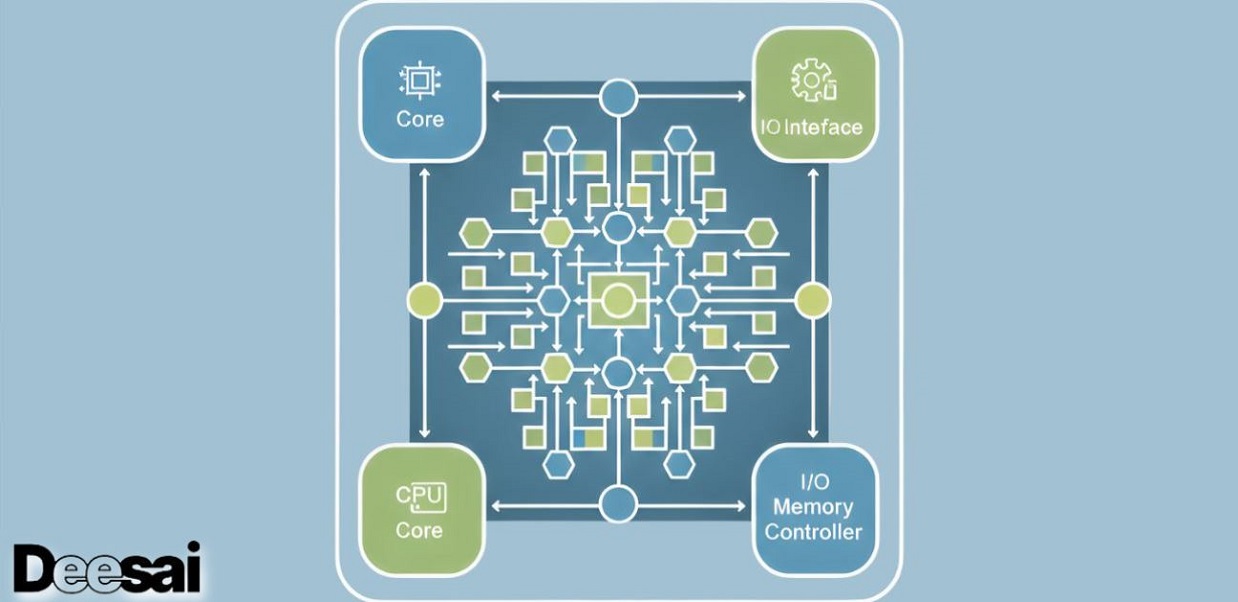

เครือข่ายบนชิป (Network-on-Chip หรือ NoC) คือ ระบบย่อยการสื่อสารแบบมี โครงสร้าง และใช้การสวิตช์แพ็กเก็ต ซึ่งเป็นแกนหลักของ SoC ที่ซับซ้อน แตกต่างจากการเดินสาย ad-hoc ทั่วโลก NoC ใช้โครงสร้างเครือข่ายที่เป็นระบบ กล่าวคือ เครือข่ายของเราเตอร์และลิงก์ทาง กายภาพเชื่อมต่อกัน เร้าเตอร์แต่ละตัวเป็นองค์ประกอบแบบโมดูลที่เรียบง่าย ทำหน้าที่ส่งแพ็กเก็ต ข้อมูลจากโหนดต้นทาง (เช่น แกน CPU) ไปยังโหนดปลายทาง (เช่น ตัวควบคุมหน่วยความจำ) ผ่านอัลกอริธึม มากำหนดเส้นทางที่กำหนดไว้ล่วงหน้า แกน IP เชื่อมต่อกับเครือข่ายนี้ผ่าน อินเทอร์เฟซมาตรฐานที่เรียกว่า อินเทอร์เฟซเครือข่าย (Network Interfaces หรือ NIs) ซึ่งทำหน้าที่แปลงข้อมูลที่สำคัญระหว่างโปรโตคอลแบบธุรกรรมของแกนและกระแสข้อมูลแบบ แพ็กเก็ตของเครือข่าย การแยกการคำนวณออกจากการสื่อสารนี้เป็นหัวใจสำคัญของการออกแบบ NoC

ข้อได้เปรียบหลักเหนือการเชื่อมต่อแบบดั้งเดิม

แนวคิด NoC นำเสนอประโยชน์ที่สำคัญหลายประการซึ่งจำเป็นสำหรับ SoC สมัยใหม่ ประการแรก คือ ความสามารถในการขยายขนาด: การเพิ่มบล็อก IP ใหม่ทำได้ง่ายเพียงแค่เชื่อม ต่อกับเร้าเตอร์ที่ใกล้ที่สุด จึงลดความแออัดของสายไฟโดยรวม และทำให้การออกแบบ ทางกายภาพง่ายขึ้น ประการที่สอง คือ การทำงานพร้อมกัน: เครือข่ายรองรับการสื่อสาร แบบจุดต่อจุดพร้อมกันหลายรายการอย่างเป็นธรรมชาติ จึงเพิ่มแบนด์วิดท์โดยรวมอย่างมาก เมื่อเทียบกับสื่อที่ใช้ร่วมกัน ประการที่สาม คือ ความเป็นโมดูลและการนำกลับมาใช้ใหม่: เราเตอร์มาตรฐานและส่วนประกอบ NI สามารถทำซ้ำได้ ทำให้วงจรการออกแบบคาดการณ์ได้ และอำนวยความสะดวกในการนำ IP กลับมาใช้ใหม่ใน SoC รุ่นต่างๆ สุดท้ายคือ ประสิทธิภาพ การใช้พลังงานได้รับการปรับปรุง เนื่องจากข้อมูลเดินทางผ่านส่วนต่างๆ ในเวลาสั้นกว่า และมีการจัดการ และสามารถใช้เทคนิคขั้นสูง เช่น การปิดสัญญาณนาฬิกาและการปรับขนาด แรงดันไฟฟ้ากับพื้นที่เครือข่ายที่ไม่ได้ใช้งานได้

มิติการออกแบบที่สำคัญของ NoC

การออกแบบ NoC ที่มีประสิทธิภาพเกี่ยวข้องกับการเพิ่มประสิทธิภาพพารามิเตอร์ ที่พึ่งพาซึ่งกันและกันหลายประการ โครงสร้างเครือข่าย—การจัดวางทางกายภาพ และ ตรรกะของเราเตอร์และลิงก์—มีความสำคัญอย่างยิ่ง โครงสร้างเครือข่ายทั่วไป ได้แก่ เมช 2 มิติ (แบบง่ายและปกติ) วงแหวน (ความหน่วงต่ำสำหรับขนาดเล็ก) และทอรัส (พร้อมลิงก์แบบวนรอบ) การเลือกโครงสร้างเครือข่ายส่งผลต่อความหน่วง ปริมาณงาน และพื้นที่ อัลกอริทึมการกำหนด เส้นทางจะกำหนดเส้นทางที่แพ็กเก็ตใช้ การกำหนดเส้นทางตามลำดับมิติ (X-Y) นั้นง่ายและ ปราศจาก deadlock แต่ไม่สามารถปรับได้ การกำหนดเส้นทางแบบปรับตัวได้สามารถ หลีกเลี่ยงพื้นที่แออัดได้ แต่มีความซับซ้อนกว่า การควบคุมการไหลจะจัดการการจัดสรรทรัพยากร บัฟเฟอร์และลิงก์ การควบคุมการไหลแบบอิงเครดิตนั้นแพร่หลาย เนื่องจากมีประสิทธิภาพ และหลีกเลี่ยงภาวะdeadlock อีกทั้งกลไกคุณภาพของบริการ (QoS) มีความสำคัญอย่างยิ่ง โดยให้ช่องสัญญาณที่มีลำดับความสำคัญสำหรับทราฟฟิกที่ไวต่อความหน่วง (เช่น สตรีมเสียง/วิดีโอ) ในขณะเดียวกันก็รับประกันความเป็นธรรมสำหรับข้อมูลแบบ best-effort

แนวโน้มที่กำลังเกิดขึ้นและทิศทางในอนาคต

ในขณะที่ SoCs พัฒนาขึ้น เทคโนโลยี NoC ก็ก้าวหน้าอย่างต่อเนื่อง การรวมคอร์ ที่แตกต่างกัน (CPU, GPU, ตัวเร่งความเร็ว AI) ทำให้เกิดรูปแบบการรับส่งข้อมูลที่ซับซ้อน และไม่สม่ำเสมอ ซึ่งผลักดันความต้องการ NoC ที่ชาญฉลาดและรับรู้แอปพลิเคชันได้มากขึ้น ระบบที่ใช้ชิปเล็ตและการ multi-die integration ขยายแนวคิด NoC ไปสู่ "เครือข่ายในแพ็คเกจ" (NiP) ซึ่งต้องการลิงก์ระหว่าง Inter-die links ที่มีแบนด์วิดท์สูงมากและมีความหน่วงต่ำ การวิจัยเกี่ยวกับ NoC แบบออปติคอล โดยใช้ซิลิคอนโฟโตนิกส์รับประกันได้ว่า จะได้ประโยชน์ อย่างมหาศาลในด้านแบนด์วิดท์และประสิทธิภาพการใช้พลังงานสำหรับการเคลื่อนย้ายข้อมูล นอกจากนี้ การเพิ่มขึ้นของภาระงานการเรียนรู้ของเครื่องยังเป็นแรงบันดาลใจให้เกิด NoC ที่มีการสนับสนุนเฉพาะสำหรับรูปแบบการสื่อสารแบบรวมกลุ่ม เช่น มัลติแคสต์และการลดขนาด ซึ่งช่วยเพิ่มประสิทธิภาพการไหลของข้อมูลสำหรับตัวเร่งความเร็ว AI

สรุป

เครือข่ายบนชิป (Network-on-Chip หรือ NoC) ได้พิสูจน์ตัวเองแล้วว่า เป็นโครงสร้างพื้นฐานการสื่อสารที่ขาดไม่ได้สำหรับ SoC แบบมัลติคอร์และหลายคอร์ โดยการประยุกต์ใช้หลักการจากเครือข่ายคอมพิวเตอร์มาสู่โดเมนบนชิป ทำให้ สามารถแก้ปัญหาความสามารถในการขยายขนาดของการเชื่อมต่อที่สำคัญ ซึ่งเป็น อุปสรรคต่อสถาปัตยกรรมรุ่นก่อนๆ แนวทางแบบมีโครงสร้าง และการสวิตช์แพ็กเก็ต ช่วยให้ทำงานพร้อมกันได้สูง มีความเป็นโมดูลาร์ และประหยัดพลังงาน ซึ่งเป็นสิ่งที่จำเป็น สำหรับแอปพลิเคชันในปัจจุบัน ตั้งแต่อุปกรณ์เคลื่อนที่ไปจนถึงเซิร์ฟเวอร์คลาวด์ เมื่อความ ซับซ้อนของ SoC เพิ่มขึ้นพร้อมกับการแพร่หลายของตัวเร่งความเร็วเฉพาะทาง และการออก แบบใช้ชิปเล็ต บทบาทของ NoC จึงมีความสำคัญและซับซ้อนมากขึ้นเรื่อยๆ อีกทั้งมี การพัฒนาอย่างต่อเนื่องเพื่อตอบสนองความต้องการด้านประสิทธิภาพ ประสิทธิผล และความคล่องตัวในการออกแบบในยุคซิลิคอน

ผลิตภัณฑ์

January 12, 2026

เครือข่ายบนชิป (Network-on-Chip หรือ NoC): การเชื่อมต่อสำหรับ SoC แบบมัลติคอร์

เรียนรู้ว่า Network-on-Chip (NoC) มอบโครงสร้างพื้นฐานความเร็วสูงสำหรับโปรเซสเซอร์มัลติคอร์สมัยใหม่ได้อย่างไร

by

นักเขียนบทความ