ผลิตภัณฑ์

19

Jan

แรงดันไฟฟ้าต่ํา การออกแบบกระแสไฟสูงสําหรับโซลูชัน SoC, FPGA และไมโครโปรเซสเซอร์ขั้นสูง

เรียนรู้วิธีจัดการกับความต้องการพลังงานที่ซับซ้อนของโซลูชันซิลิกอนความเร็วสูงที่ทันสมัย

บทคัดย่อ

บทความนี้กล่าวถึงความต้องการโซลูชันด้านพลังงานขั้นสูงในการใช้งานไฮเทคต่างๆ แอปพลิเคชันเหล่านี้ต้องการแหล่งจ่ายไฟแรงดันต่ําหลายตัวสําหรับส่วนประกอบต่างๆ เช่น DDR, คอร์ และอุปกรณ์ I/O และความหนาแน่นที่เพิ่มขึ้นของการรวมเซมิคอนดักเตอร์ทําให้ไมโครโปรเซสเซอร์ใช้พลังงานมากขึ้น มีความต้องการที่เพิ่มขึ้นสําหรับความสามารถในการส่งข้อมูลทางไกลเพื่อตรวจสอบพารามิเตอร์ เช่น แรงดันไฟฟ้า กระแส และอุณหภูมิ บทความนี้แนะนําการออกแบบตัวควบคุมแบบสเต็ปดาวน์แบบสองเฟสที่รวมฟังก์ชันการจัดการระบบไฟฟ้าแบบดิจิทัล การออกแบบเน้นการบรรลุเป้าหมายที่สําคัญ เช่น ขนาด ประสิทธิภาพ ความเสถียรของลูป และการตอบสนองชั่วคราว

บทนํา

ทุกวันนี้แอปพลิเคชันอุตสาหกรรมยานยนต์เซิร์ฟเวอร์โทรคมนาคมและดาต้าคอมต้องการโซลูชันระบบบนชิป (SoC), FPGA และไมโครโปรเซสเซอร์ขั้นสูง โซลูชันเหล่านั้นต้องการอุปกรณ์จ่ายไฟแรงดันต่ําหลายตัว รวมถึง 1.1 V สําหรับ DDR, 0.8 V สําหรับแกน และ 3.3 V/1.8 V สําหรับอุปกรณ์ I/O เนื่องจากการรวมเซมิคอนดักเตอร์ที่มีความหนาแน่นสูงไมโครโปรเซสเซอร์จึงใช้พลังงานมากกว่าและต้องการกระแสไฟมากขึ้น

นอกจากนี้ยังมีความต้องการสูงสําหรับการวัดและส่งข้อมูลทางไกลโดยใช้ FPGA หรือไมโครโปรเซสเซอร์ที่สามารถตรวจสอบแรงดันไฟฟ้ากระแสอุณหภูมิและพารามิเตอร์อุปกรณ์อื่น ๆ เพื่อลดความซับซ้อนของโซลูชันการออกแบบ IC พลังงานแบบอะนาล็อกที่มี I 2C/PMBus® ในตัวสามารถตรวจสอบพารามิเตอร์หลักและควบคุมการวัดและส่งข้อมูลทางไกลได้

ด้วยเหตุนี้ โซลูชันด้านพลังงานจึงต้องรวมเข้ากับ I2C/ PMBus เพื่อเปิดใช้งานการอ่านย้อนกลับทางไกลและความสามารถในการตั้งโปรแกรมของตัวควบคุมในขณะเดียวกันก็ให้ความสามารถในปัจจุบันที่สูงขึ้น ชิ้นส่วนหลายเฟสที่ให้ประสิทธิภาพสูงที่ตอบสนองความต้องการเหล่านั้นกําลังเป็นที่นิยมมากขึ้น ในบทความนี้ เราจะแนะนําแนวคิดการออกแบบสําหรับตัวควบคุมสเต็ปดาวน์แบบสองเฟส ที่สามารถส่งกระแสไฟต่อเนื่องได้สูงสุด 40 A จากทั้งสองช่องสัญญาณ และโหลดสูงสุด 30 A จากแต่ละช่องสัญญาณ นอกจากนี้ยังรวมฟังก์ชันการจัดการระบบไฟฟ้าแบบดิจิทัลที่ช่วยให้สามารถตั้งโปรแกรมและการวัดและส่งข้อมูลทางไกลด้วยอินเทอร์เฟซอนุกรมที่สอดคล้องกับ PMBus/I 2C ต้องใช้ความระมัดระวังเพื่อให้บรรลุเป้าหมายการออกแบบของขนาด ประสิทธิภาพ ความเสถียรของลูป และการตอบสนองชั่วคราว

เหตุใดประสิทธิภาพจึงมีความสําคัญ

สําหรับแรงดันไฟฟ้าต่ําและแหล่งจ่ายไฟกระแสสูง เช่น แอปพลิเคชันต้องใช้ 1 V, 30 A จากแหล่งจ่ายไฟ 12 V ประสิทธิภาพ 80% นําไปสู่การสูญเสียทั้งหมด 7.5 W การสูญเสียเหล่านั้นจะส่งผลให้พลังงานความร้อนและอุณหภูมิเพิ่มขึ้นสําหรับ IC และตัวเหนี่ยวนํา เนื่องจากอุณหภูมิแวดล้อมของศูนย์ข้อมูลมักจะสูงกว่าอุณหภูมิห้องการสูญเสียที่เพิ่มขึ้นจะทําให้อุณหภูมิเพิ่มขึ้นสําหรับ IC และใกล้เคียงกับขีดจํากัดการปิดระบบระบายความร้อนของ IC มากขึ้น (โดยปกติคือ 150°C) สิ่งนี้มีความสําคัญมากขึ้นสําหรับการใช้งาน point-of-load (POL) เนื่องจากตัวแปลง DC-to-DC มักจะอยู่ใกล้กับไมโครโปรเซสเซอร์ที่ร้อนมาก

ในส่วนต่อไปนี้ จะมีหลายวิธีเพื่อปรับปรุงประสิทธิภาพสําหรับการออกแบบชิ้นส่วนแรงดันต่ําและกระแสไฟสูง

การติดตาม PCB ที่โหนด SW

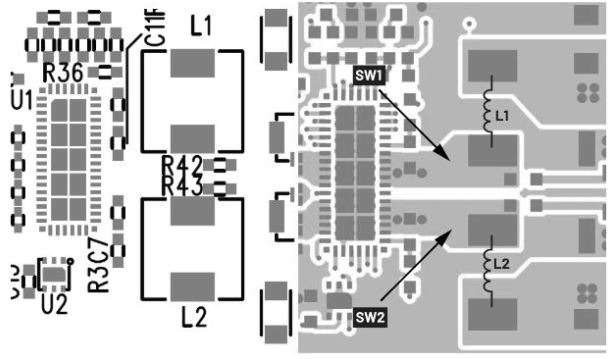

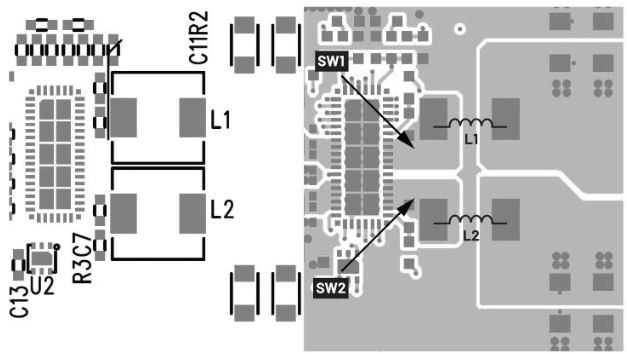

ในเวอร์ชันก่อนหน้าของการออกแบบบอร์ดสาธิตชิ้นส่วนสองเฟส ตัวเหนี่ยวนําจากเฟส 1 และเฟส 2 หันเข้าหากันดังแสดงในรูปที่ 1 ประสิทธิภาพของ EMI จะดีกว่าหากตัวเหนี่ยวนําอยู่ในลักษณะนี้ ข้อเสียของการวางแนวนี้คือโหนดสวิตชิ่ง (SW) จะมีร่องรอยที่ค่อนข้างยาวส่งผลให้สูญเสียการติดตาม PCB มากขึ้นโดยเฉพาะอย่างยิ่งในสภาวะโหลดหนักเนื่องจากการสูญเสียการนําไฟฟ้าเป็นสัดส่วนกับกําลังสองของค่าปัจจุบัน (P = I 2R)

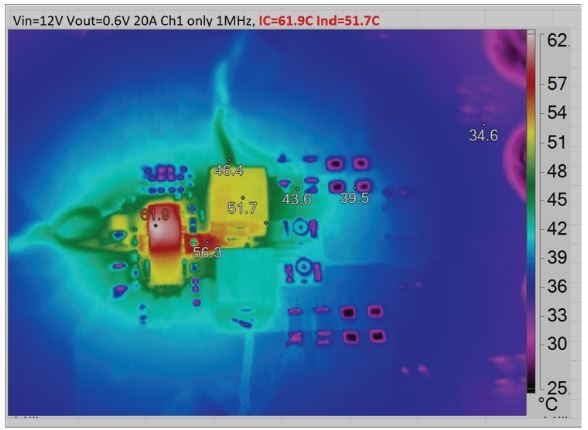

รูปที่ 2 แสดงภาพความร้อนที่สภาวะโหลด 20 A โหนดสวิตชิ่งร้อนมากโดยมีอุณหภูมิเพิ่มขึ้นเกือบเท่ากับ IC การออกแบบที่เหมาะสมสามารถปรับปรุงการสูญเสียที่เกิดจากการติดตาม PCB

ในการตั้งค่าการทดสอบของรูปที่ 3 PCB จะถูกตัดออกและตัวเหนี่ยวนํา Ch1 ถูกย้ายเข้าใกล้ IC มากขึ้นเพื่อลดการติดตามโหนด SW

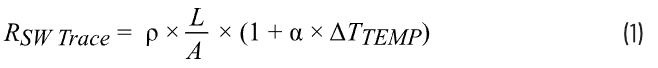

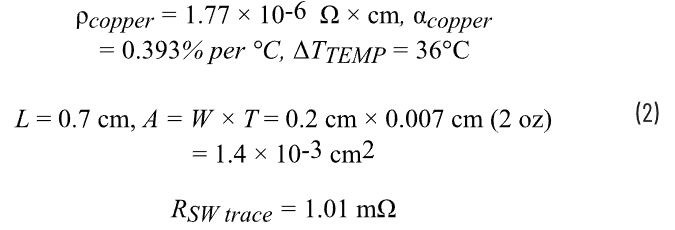

ขึ้นอยู่กับความหนาและความยาวของทองแดงของร่องรอย PCB โหนด SW มีความต้านทาน DC ของ:

ที่ไหน:

การสูญเสียทั้งหมดคือ:

ที่ไหน:

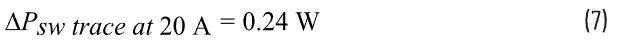

สําหรับสภาวะโหลด 20 A การสูญเสียที่คาดว่าจะสร้างขึ้นจากโหนด SW คือ:

หลังจากลดร่องรอย SW L = 0.3 ซม. การสูญเสียที่ดีขึ้นคือ:

การปรับปรุงการสูญเสียที่คาดหวังตามการคํานวณคือ:

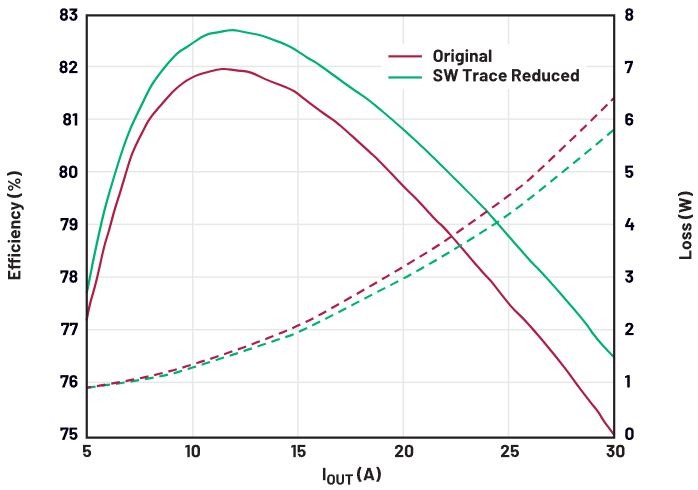

รูปที่ 4 แสดงการปรับปรุงประสิทธิภาพตามผลการทดสอบ การปรับปรุงการสูญเสียคือ 0.22 W สําหรับ 20 A และ 0.53 W สําหรับสภาวะโหลด 30 A

เมื่อโหลดเพิ่มขึ้นความแตกต่างของประสิทธิภาพจะมากขึ้นซึ่งหมายความว่าการสูญเสียการนําไฟฟ้า (P = I 2R) ที่ร่องรอย PCB นี้จะถูกครอบงํา ในสภาวะโหลดเต็มที่สามารถเพิ่มประสิทธิภาพได้ 1.5% ไม่สามารถเคลื่อนย้ายตัวเหนี่ยวนําเข้าใกล้ IC ได้ ดังนั้นในบอร์ด Rev 2 ตัวเหนี่ยวนําจะหมุน 90° เพื่อให้หันไปทาง IC เพื่อลดความยาวร่องรอย SW ดังแสดงในรูปที่ 5

CIN เพิ่มเติมเพื่อระงับเสียงเรียกเข้า VIN

ในการศึกษาของเราตัวเก็บประจุอินพุตยังมีผลกระทบอย่างมากต่อประสิทธิภาพและความเสถียรของการใช้งานแรงดันไฟฟ้าต่ําและกระแสไฟสูง วิศวกรมักเพิกเฉยต่อความสําคัญของการออกแบบตัวเก็บประจุอินพุตและใช้ประสบการณ์ก่อนหน้านี้ในการวางตัวเก็บประจุอินพุต บางครั้ง จํากัด ด้วยขนาดโซลูชัน PCB ทั้งหมด วิศวกรอาจใส่ตัวเก็บประจุอินพุตน้อยลง ซึ่งนําไปสู่ความไม่เสถียรและการสูญเสียมากขึ้น

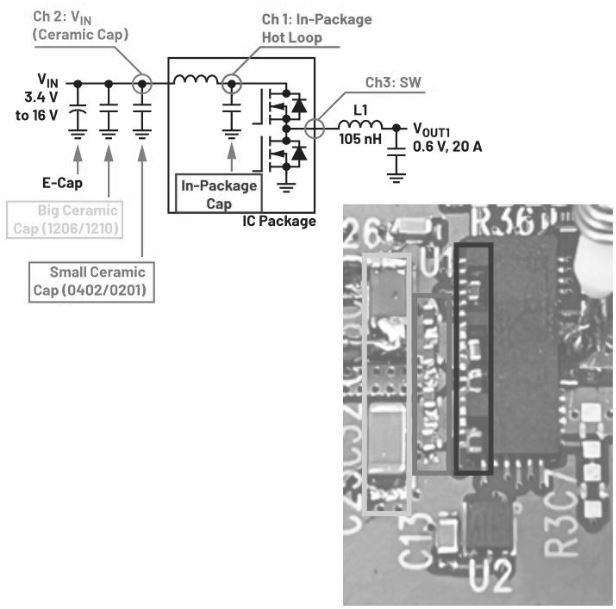

รูปที่ 6 จากซ้ายไปขวาแสดงฝาปิดไฟฟ้าสําหรับปลั๊กร้อนและระงับกระแสไฟกระชากฝาเซรามิกขนาดใหญ่ (โดยปกติจะมีขนาด 1210 หรือ 1206) ใช้สําหรับลดระลอกคลื่นกระแสไฟเข้าและฝาเซรามิกขนาดเล็ก (ขนาด 0402 หรือ 0201) ใช้สําหรับลดระลอกคลื่นความถี่สูง นอกเหนือจากนี้ สําหรับเทคโนโลยี Silent Switcher® 2 ตัวเก็บประจุคู่หนึ่งจะถูกฝังอยู่ในแพ็คเกจเพื่อลดสัญญาณรบกวนความถี่สูงของ SW และโอเวอร์ชูต ภาพทางด้านขวาของรูปที่ 6 แสดงตัวเก็บประจุเซรามิก 1206 สองตัว (สีเหลือง) ตัวเก็บประจุเซรามิก 0402 สี่ตัวนอกบรรจุภัณฑ์ (สีน้ําเงิน) และตัวเก็บประจุ 0402 สี่ตัวในบรรจุภัณฑ์ (สีแดง) โดยใช้เทคนิคการถอดห่อ มีการสลักรูในบรรจุภัณฑ์เหนือแม่พิมพ์เพื่อให้เห็นตัวเก็บประจุในบรรจุภัณฑ์เหนือพื้นผิว

ตัวเก็บประจุอินพุตเหล่านั้นจะถูกตรวจสอบพร้อมกับโหนดสวิตชิ่งเพื่อสังเกตพฤติกรรมของชุดค่าผสมตัวเก็บประจุอินพุตที่แตกต่างกัน

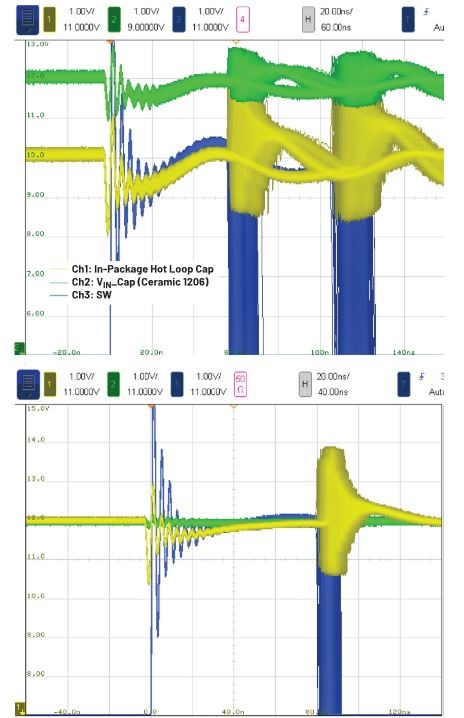

หากความจุอินพุตทั้งหมดมีขนาดเล็ก (รูปคลื่นด้านบนของรูปที่ 7) เสียงเรียกเข้าขนาดใหญ่จะปรากฏขึ้นที่รูปคลื่นของโหนด SW ในระหว่างสภาวะโหลดหนัก เนื่องจากเมื่อสวิตช์ด้านบนทํางานกระแสส่วนใหญ่จะถูกลากจากตัวเก็บประจุอินพุต ประจุทั้งหมด = ความจุคูณแรงดันไฟฟ้า (Q = CV) ดังนั้นหากความจุมีขนาดเล็กจะมีแรงดันไฟฟ้าตกคร่อมมากที่ C IN C IN พร้อมกับการเหนี่ยวนําปรสิตที่ร่องรอยอินพุตและแพ็คเกจ IC จะก่อตัวเป็นถัง LC และนําไปสู่เสียงกริ่งที่โหนดสวิตชิ่ง แรงดันไฟฟ้าตกขนาดใหญ่จะทําให้เกิดการบิดเบือนของ SW และความไม่เสถียรเมื่อมีพัลส์ขนาดเล็กตามด้วยพัลส์ขนาดใหญ่

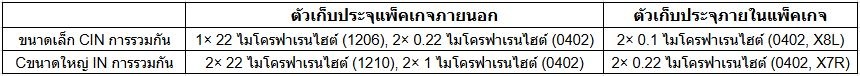

ความไม่เสถียรของการสลับสามารถปรับปรุงได้หากมีการเพิ่มความจุอินพุตมากขึ้นเพื่อระงับเสียงเรียกเข้า เมื่อเทียบกับชุดค่าผสม C IN ขนาดเล็กชุดค่าผสม CIN ขนาดใหญ่จะเพิ่มค่าความจุรวมเป็นสองเท่า ยิ่ง C IN อยู่ใกล้ด้านบนของสวิตช์มากเท่าไหร่ การปรับปรุงก็จะยิ่งมากขึ้นเท่านั้น ดังนั้นจึงเป็นการดีกว่าที่จะเพิ่มมูลค่าของตัวเก็บประจุในแพ็คเกจ ในกรณีของเรา 0.1 μF (0402, X8L) สองตัวจะเพิ่มขึ้นเป็น 0.22 μF (0402, X7R) (ดูตารางที่ 1) และการสลับจะเสถียร (รูปคลื่นด้านล่างในรูปที่ 7)

อย่างไรก็ตาม การแลกเปลี่ยนคือช่วงอุณหภูมิการทํางานสูงสุดของ IC ลดลงจาก 150°C (X8L) เป็น 125°C (X7R) บางครั้ง อุณหภูมิสูงสุดของ IC เป็นปัจจัยสําคัญที่ต้องพิจารณา เนื่องจากแอปพลิเคชันจํานวนมาก เช่น ศูนย์ข้อมูล มีอุณหภูมิแวดล้อมมากกว่า 70°C วิศวกรจําเป็นต้องใส่ใจกับสิ่งเหล่านี้เนื่องจากอุณหภูมิสูงสุดอาจเกินช่วงหากเลือกตัวเก็บประจุในแพ็คเกจ X7R

CIN ที่มากขึ้นไม่เพียงแต่ช่วยเพิ่มเสถียรภาพของการสลับ แต่ยังช่วยเพิ่มประสิทธิภาพอีกด้วย รูปที่ 8 แสดงการปรับปรุงประสิทธิภาพ ~1.4% และการลดการสูญเสีย 0.3 W หากเพิ่มตัวเก็บประจุอินพุตเพียงพอ วงแหวนและปริมาตร tag ลดลงที่ด้านอินพุตจะทําให้สูญเสียการสลับมากขึ้น เนื่องจากตัวเก็บประจุขนาด 8× 1206 มีประสิทธิภาพใกล้เคียงกับตัวเก็บประจุขนาด 2× 1210 การเลือก C IN ที่เหมาะสมที่สุดในกรณีนี้คือ 2× 22 μF พร้อมตัวเก็บประจุขนาด 1210

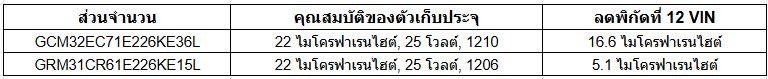

สําหรับการเลือกตัวเก็บประจุอินพุตวิศวกรควรใส่ใจกับการลดพิกัด DC เนื่องจากตัวเก็บประจุเซรามิกมีช่วงพิกัด DC ขนาดใหญ่ ตัวอย่างเช่นการเปรียบเทียบการลดพิกัด DC ของตัวเก็บประจุ 1206 และ 1210 ที่ 12 V ขนาด 1206 จะเสื่อมสภาพมากขึ้น ในตารางที่ 2 ตัวเก็บประจุ Murata สองตัวแสดงเป็นตัวอย่าง ดังนั้นจึงแนะนําให้ใช้ตัวเก็บประจุขนาด 1210 เป็นอินพุตของแหล่งจ่ายไฟแรงดันต่ําและกระแสไฟสูง

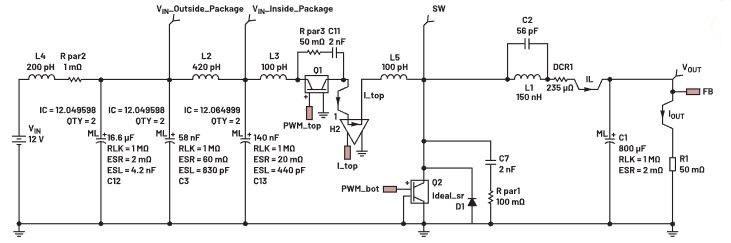

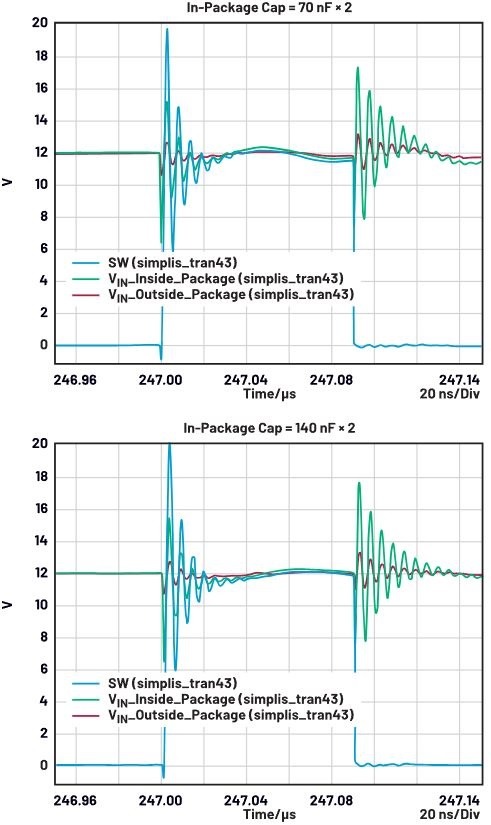

การจําลอง SIMPLIS อาจเป็นเครื่องมือที่มีประโยชน์ในการช่วยให้วิศวกรออกแบบค่าที่เหมาะสมที่สุดของ C IN ได้ดียิ่งขึ้น รูปที่ 9 แสดงตัวควบคุมบั๊กที่มีการเหนี่ยวนําปรสิตโดยประมาณตามร่องรอยกําลัง ความจุอินพุตได้รับการปรับตามการลดพิกัด DC ของตัวเก็บประจุเซรามิกที่แรงดันไฟฟ้าอินพุต 12 V วงแหวนจะได้รับการปรับปรุงหากความจุอินพุตเพิ่มขึ้นเป็นสองเท่าจาก 2× 70 nF เป็น 2× 140 nF (ดูรูปที่ 10)

สรุป

บทความนี้มุ่งเน้นไปที่การออกแบบแหล่งจ่ายไฟแรงดันต่ําและกระแสไฟสูง มีการนําสองวิธีมาใช้เพื่อปรับปรุงประสิทธิภาพในสภาวะโหลดหนัก จากจุดความร้อนที่โหนดสวิตชิ่งบน PCB ซึ่งมีอุณหภูมิเพิ่มขึ้นเกือบเท่ากับ IC เราแนะนําให้ลดความยาวร่องรอยของโหนดสวิตชิ่งโดยการเปลี่ยนทิศทางของตัวเหนี่ยวนําเพื่อลดการสูญเสีย การออกแบบความจุอินพุตอาจมีความสําคัญมาก แต่ก็ง่ายต่อการเพิกเฉย ความจุอินพุตไม่เพียงพอจะนําไปสู่ความไม่เสถียรและความไร้ประสิทธิภาพของแหล่งจ่ายไฟ วิศวกรแอปพลิเคชันจะต้องให้ความสนใจอย่างรอบคอบเพื่อปรับสมดุลปริมาณความจุอินพุตสําหรับการออกแบบแหล่งจ่ายไฟแรงดันต่ําและกระแสไฟสูง

ผลิตภัณฑ์

March 2, 2026

แรงดันไฟฟ้าต่ํา การออกแบบกระแสไฟสูงสําหรับโซลูชัน SoC, FPGA และไมโครโปรเซสเซอร์ขั้นสูง

เรียนรู้วิธีจัดการกับความต้องการพลังงานที่ซับซ้อนของโซลูชันซิลิกอนความเร็วสูงที่ทันสมัย

by

นักเขียนบทความ