ผลิตภัณฑ์

19

Jan

สถาปัตยกรรมพลังงาน Grid-to-Core ของศูนย์ข้อมูล AI

เรียนรู้ว่าสถาปัตยกรรม Grid-to-Core แก้ปัญหาความต้องการพลังงานมหาศาลของ AI สมัยใหม่ได้อย่างไร

ปริมาณงานการประมวลผลที่เพิ่มขึ้นอย่างรวดเร็วซึ่งขับเคลื่อนโดย AI กําลังผลักดันความต้องการพลังงานให้เติบโตในอัตราที่ไม่เคยมีมาก่อน โดยเกิน 50% CAGR ตั้งแต่ปี 2024 ถึง 2028 การเพิ่มขึ้นนี้กําลังผลักดันการใช้พลังงานเป็นร้อยกิกะวัตต์ และบังคับให้อุตสาหกรรมเร่งวงจรการพัฒนาแพลตฟอร์ม โดยตอนนี้ปล่อยเซิร์ฟเวอร์ใหม่ทุกๆ 12-15 เดือน แทนที่จะเป็นจังหวะ 30 เดือนแบบเดิม.

ความต้องการพลังงานในระดับ AI SoC (xPU) เพิ่มขึ้นอย่างรวดเร็วเป็นพิเศษ โดยแซงหน้าหลายกิโลวัตต์สําหรับอุปกรณ์ที่เข้าสู่การผลิตในช่วงต้นปี 2026"กฎของมัวร์" ในยุค AI ของการประมวลผลแบบขนานกําลังเพิ่มความต้องการพลังงานเป็นสองเท่าต่อปี ซึ่งแซงหน้าแนวโน้มการเติบโตในอดีต.

ในระดับแร็ค สิ่งนี้ทําให้เกิดความต้องการแนวทางการกระจายพลังงานที่แตกต่างกันโดยพื้นฐานซึ่งสามารถรองรับระดับโหลดที่สูงขึ้นมากตัวอย่างเช่น แร็ค NVL72 ที่ใช้ Nvidia Blackwell ในปัจจุบันใช้พลังงานประมาณ 130 กิโลวัตต์ แต่รุ่นต่อไปคาดว่าจะมีกําลังไฟประมาณ 300 กิโลวัตต์.

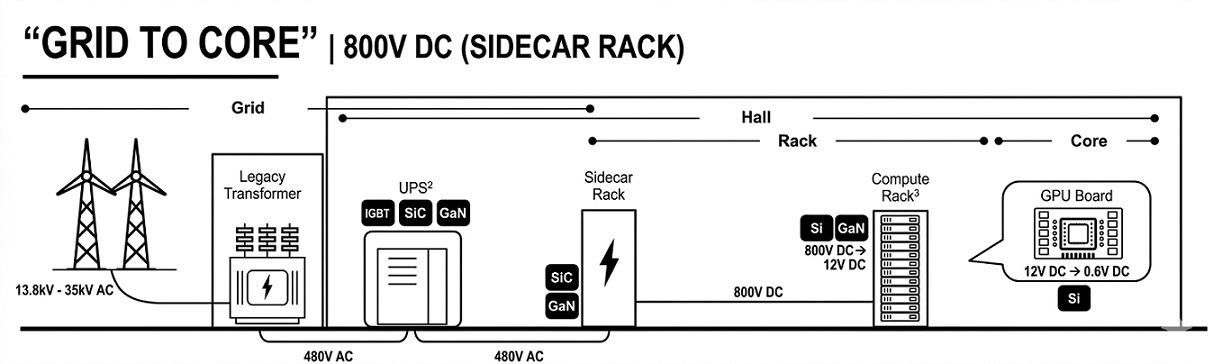

ด้วยระบบ NLV144 ที่ใช้ Rubin มีแนวโน้มที่จะเพิ่มความหนาแน่นของ GPU เป็นสองเท่า และการกําหนดค่า NVL576 ในอนาคตเกือบ 1 MW ต่อแร็ค การเพิ่มแรงดันไฟฟ้าในการกระจายจึงกลายเป็นสิ่งสําคัญเพื่อลดการสูญเสียสิ่งนี้ขับเคลื่อนการเปลี่ยนจากบัส OCP 48 V ที่ได้มาตรฐานแบบยาวเป็นบัส 800 V DC ซึ่งกระจายโดยใช้สายไฟสองเส้น หรือในที่สุดก็เป็นระบบ ±400 V บวกสายดิน (รูปที่.1).

เมื่อพลังงานในชั้นวางคอมพิวท์เพิ่มขึ้นและแพร่กระจายไปทั่วดาต้าเซ็นเตอร์ จึงไม่สามารถวางเวที AC/DC ไว้ในชั้นวางเดียวกันได้อีกต่อไปแร็ค "SideCar" เฉพาะใหม่กําลังเกิดขึ้นเพื่อแปลง 415 Vac ขาเข้าเป็น 800 V DC การกระจาย 415 Vac นี้มีต้นกําเนิดมาจาก PDU ของศูนย์ข้อมูล ผ่าน AC UPS และป้อนโดยแหล่งจ่ายไฟ 480 Vac จากแผงสวิตช์หลักที่เชื่อมโยงกับกริดแรงดันปานกลาง (13.8–35 kVac).

อุตสาหกรรมตั้งแต่การออกแบบอ้างอิง OEM ไปจนถึงการออกแบบ ODM ใหม่ที่ขับเคลื่อนด้วยไฮเปอร์สเกลเลอร์และผู้ผลิตพาวเวอร์ซัพพลายกําลังเปลี่ยนไปใช้สถาปัตยกรรมใหม่นี้โดยรวมแนวทางแบบไฮบริดและแบบเดิมจะยังคงอยู่ชั่วคราว รวมถึงชั้นวางที่ยังคงรับอินพุต AC และสร้าง 800 V สําหรับจํานวน GPU ที่เล็กลง แต่ระบบนิเวศกําลังมาบรรจบกันไปสู่โมเดลมาตรฐานที่สอดคล้องกับความคิดริเริ่มของ OCP.

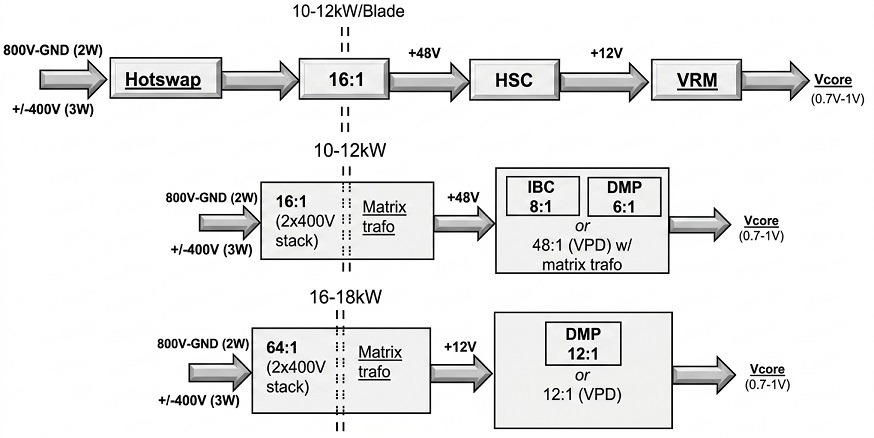

ภายในชั้นวางการประมวลผล โครงสร้างพื้นฐานที่มีอยู่ยังคงอาศัย 48 V ซึ่งจําเป็นต้องใช้ตัวแปลงความหนาแน่นสูงที่มีประสิทธิภาพสูงเพื่อลดระดับจาก 800 V Renesas มีส่วนช่วยในการออกแบบอ้างอิง 6 กิโลวัตต์สําหรับสถาปัตยกรรมเบลด 12 กิโลวัตต์ที่สร้างขึ้นบน 650 V GaN FET ในบรรจุภัณฑ์ TOLT และ 80 V MOSFET ใน QFN 5×6 มม. การใช้โทโพโลยี LLC ที่ไม่มีการควบคุม DTX ที่สลับสูงกว่า 900 kHz การออกแบบให้ประสิทธิภาพสูงสุดมากกว่า 98% และความหนาแน่นของพลังงานมากกว่า 2.5 กิโลวัตต์/นิ้ว³เช่นเดียวกับ Renesas PoC ทั้งหมด ซึ่งรวมถึงแผนผัง เค้าโครง BOM และข้อมูลการทดสอบแบบเต็ม.

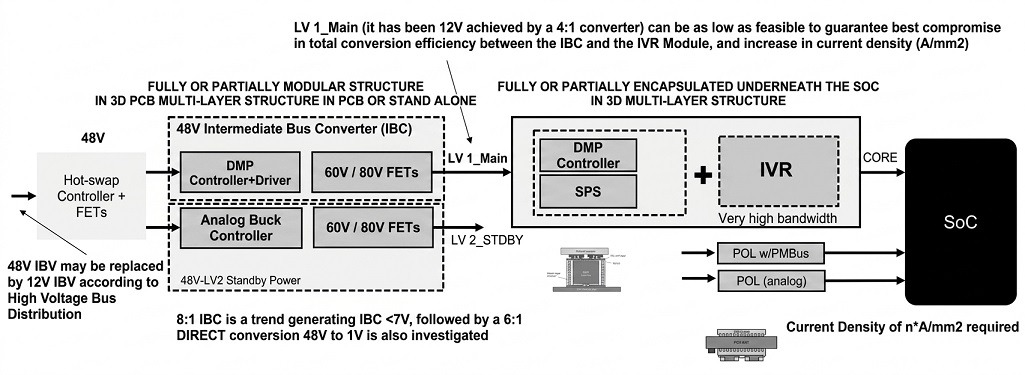

ต่ํากว่า 48 V สถาปัตยกรรมส่วนใหญ่ยังคงไม่เปลี่ยนแปลงในตอนนี้อย่างไรก็ตาม กระแสโหลด SoC ที่พุ่งสูงขึ้นซึ่งเข้าใกล้ 4 kA ต้องใช้วิธีการส่งมอบใหม่ (รูปที่ 3 และ 4)การกําหนดเส้นทางพลังงานด้านข้างแบบดั้งเดิมไม่เพียงพออีกต่อไป Vertical Power Delivery (VPD) กําลังเกิดขึ้น ซึ่งสามารถทําได้ผ่านขั้นตอนพลังงานที่มีจํานวนเฟสสูงขนาดกะทัดรัดหรือโดยการรวมตัวเหนี่ยวนําในโครงสร้าง 3 มิติ.

Renesas รองรับสิ่งนี้ด้วยคอนโทรลเลอร์หลายเฟสแบบดิจิทัลเต็มรูปแบบที่นําเสนออินเทอร์เฟซแบบมัลติโปรโตคอล ลูปควบคุมสูงสุดสี่ลูป และประสิทธิภาพชั่วคราวระดับบนสุดด้วย TLVR เสริมสิ่งเหล่านี้คือโมดูล Smart Power Stage ที่ให้ความเร็วสูงสุดถึง 100 A ต่อเฟส ซึ่งมีให้เลือกในแพ็คเกจหลายยูนิตแบบรวมหรือโครงสร้าง 3 มิติแบบบูรณาการ ทําให้โซลูชัน VPD แบบเฟสเดนซ์มีความหนาแน่นของกระแสไฟ 2 A/mm².

สิ่งเหล่านี้ได้รับการสนับสนุนโดยระบบนิเวศแบบ end-to-end รวมถึงการจําลองก่อนเค้าโครง การวิเคราะห์ PDN เครื่องมือฮาร์ดแวร์ ตัวแทรก การปรับแต่ง การวัด และวิธีการตรวจสอบความถูกต้องโซลูชันโมดูลาร์ขั้นสูงกําลังอยู่ในระหว่างการพัฒนา โดยรวมขั้นตอนการแปลงเพิ่มเติมในขณะที่ยังคงเปิดใช้งาน VPD โดยใช้ประโยชน์จากนวัตกรรม เช่น IVR เพื่อการสลับที่เร็วขึ้นและการควบคุมขั้นตอนสุดท้ายที่มีแบนด์วิดท์สูง.

การอภิปรายทางสถาปัตยกรรมที่สําคัญประการหนึ่งเกี่ยวข้องกับอนาคตของราง 12 V ระดับกลางที่ปัจจุบันได้มาจาก 48 V โดยใช้ IBC 4:1 (รูปที่ 2)เพื่อปรับปรุงประสิทธิภาพและความหนาแน่นของกระแสในขั้นตอนหลายเฟสสุดท้าย โดยเฉพาะอย่างยิ่งเมื่อใช้โหนดซิลิกอนแรงดันต่ําขั้นสูง แรงดันไฟฟ้าระดับกลางนี้อาจลดลง.

Renesas นําเสนอตัวแปลง Hybrid Switched-Capacitor (HSC) ประสิทธิภาพสูงที่มีประสิทธิภาพเกิน 98%การใช้การออกแบบสวิตช์ 8 ตัว สิ่งเหล่านี้สามารถสร้าง 6 V ที่ประสิทธิภาพสูงสุดถึง 97% ขึ้นอยู่กับแนวทางการกํากับดูแล Renesas ยังได้เปิดตัวการออกแบบอ้างอิงสําหรับการแปลงนี้.

อีกทางหนึ่ง บั๊กหลายเฟสที่ใช้ GaN 100 V สามารถเพิ่มความถี่การสลับเพื่อลดขนาดตัวแปลงได้อย่างมาก Renesas ได้สาธิตโซลูชัน 48 V ที่ให้กําลังสูงสุด 3 กิโลวัตต์ด้วยความหนาแน่นเกือบ 1 กิโลวัตต์/นิ้ว³ ทํางานในโหมด 8 เฟสลงถึง 6 V หรือโหมด 4 เฟสที่ 12 V พร้อมความยืดหยุ่นในการควบคุมแบบดิจิตอล.

คาดว่าจะมีการเพิ่มประสิทธิภาพทางสถาปัตยกรรมเพิ่มเติมเมื่อโมเดลการกระจาย 800 V เติบโตเต็มที่บัส 48 V ภายในภายในเบลด xPU สามารถกําจัดออกได้ทั้งหมด แทนที่ด้วยการแปลงอัตราส่วนสูงโดยตรงที่คล้ายกับขั้นตอน 16:1 ที่มีอยู่ Renesas ได้สร้างการออกแบบอ้างอิง 6 กิโลวัตต์ 800 Vto12 V (64:1) โดยใช้โทโพโลยี DTX ซึ่งสามารถปรับขนาดได้ตามระดับพลังงานที่สูงขึ้นมาก ซึ่งอาจอยู่ที่ประมาณ 20 กิโลวัตต์ ซึ่งคาดว่าจะใช้สําหรับใบมีด AI ในอนาคต เนื่องจากการใช้ xPU ยังคงเพิ่มขึ้นอย่างต่อเนื่อง.

เทคโนโลยี GaN ยังคงเป็นตัวขับเคลื่อนที่สําคัญในขั้นตอนพลังงานที่มีความหนาแน่นสูงเหล่านี้ลักษณะ widebandgap กําลังเร่งการเติบโตของเนื้อหาพลังงานในศูนย์ข้อมูลได้เร็วขึ้นและมากกว่า SiC ในหลาย ๆ ส่วน โดยเฉพาะอย่างยิ่งที่ GaN สามารถทดแทนซิลิคอน MOSFET ได้เมื่อ GaN พัฒนาไปสู่การทํางานที่มีแรงดันไฟฟ้าต่ําและมีประสิทธิภาพสูงขึ้น การเจาะเข้าไปในการจ่ายพลังงานแบบ near-core จะขยายตัว ช่วยเพิ่มความหนาแน่นโดยไม่ลดทอนประสิทธิภาพ.

ในชั้นวางไซด์คาร์ AC/DC ซึ่งปัจจุบันถูกครอบงําโดยอุปกรณ์ SiC 1200 V องค์ประกอบที่เกิดขึ้นใหม่คือสวิตช์ GaN แบบสองทิศทาง 650 V สวิตช์สี่ควอแดรนต์ที่เกือบจะเหมาะนี้ช่วยให้โทโพโลยีแบบขั้นตอนเดียวและลดความซับซ้อนของสถาปัตยกรรมส่วนหน้า เช่น วงจรเรียงกระแสแบบ T-type หรือเวียนนาช่วยลดความหนาแน่นและต้นทุนโดยการแทนที่การกําหนดค่าอุปกรณ์แบบ back-to-back แบบเดิม.

อุปกรณ์ SiC แรงดันสูง (>1.2 kV) จะมีบทบาทสําคัญในระบบหม้อแปลงโซลิดสเตต (SST) โดยที่ไฟฟ้ากระแสสลับแรงดันปานกลางจากกริดจะเข้าสู่ห้องพลังงานของศูนย์ข้อมูลและถูกแปลงเป็น 800 V DC โดยตรงสําหรับการกระจายระดับห้องโถงวิธีการที่ใช้ SST นี้ช่วยขจัดหม้อแปลง สวิตช์เกียร์ และ PDU ขนาดใหญ่ ซึ่งช่วยลดการใช้ทองแดงได้อย่างมาก เนื่องจากสายเคเบิล 800 V DC สามารถรับพลังงานได้ประมาณ 1.5× ของสายเคเบิล 415 Vac.

การพัฒนาที่สําคัญอีกประการหนึ่งคือการเปลี่ยนแปลงในสถาปัตยกรรมการจัดเก็บพลังงานจากการสํารองข้อมูลดีเซลที่ใช้ AC ไปสู่การจัดเก็บข้อมูล 800 V DC แบบกระจายที่รวมอยู่ในสภาพแวดล้อมของศูนย์ข้อมูลตัวเก็บประจุกําลังสูงหรือระบบ supercap ที่อยู่ใกล้กับชั้นวางคอมพิวเตอร์จะรองรับความต้องการพลังงานในระยะสั้น โดยรวมตัวแปลง DC/DC ตัวควบคุม และไดรเวอร์แบบสองทิศทางเพื่อจัดการการไหลของพลังงานในระดับโรงงาน การจัดเก็บแบตเตอรี่ MV และการสร้างการสํารองข้อมูลในสถานที่จะกลายเป็นสิ่งสําคัญในการสร้างความมั่นใจในการทํางานอย่างต่อเนื่องของศูนย์ข้อมูลที่เน้น AI.

ผลิตภัณฑ์

May 4, 2026

สถาปัตยกรรมพลังงาน Grid-to-Core ของศูนย์ข้อมูล AI

เรียนรู้ว่าสถาปัตยกรรม Grid-to-Core แก้ปัญหาความต้องการพลังงานมหาศาลของ AI สมัยใหม่ได้อย่างไร

by

นักเขียนบทความ