ผลิตภัณฑ์

19

Jan

Carry Look Ahead Adder – วงจรตารางความจริงและการใช้งาน

มาเรียนรู้ Carry-Lookahead Adder: วงจร ตารางความจริง และการใช้งานจริง

ระบบดิจิทัลประเภทต่างๆ ถูกสร้างขึ้นจากการกําหนดค่าเครือข่ายพื้นฐานเพียงไม่กี่ประเภท เช่น AND gate, NAND gate, Or gate เป็นต้น วงจรพื้นฐานเหล่านี้ถูกนํามาใช้ซ้ําแล้วซ้ําอีกในการผสมผสานโทโพโลยีต่างๆ นอกเหนือจากการใช้ตรรกะแล้วระบบดิจิทัลยังต้องจัดเก็บเลขฐานสองด้วย สําหรับเซลล์หน่วยความจําเหล่านี้ หรือที่เรียกว่า FLIP-FLOP ได้รับการออกแบบ เพื่อทําหน้าที่บางอย่าง เช่น การบวกไบนารี ดังนั้นในการทําหน้าที่ดังกล่าวการรวมกันของลอจิกเกตและ FLIP-FLOP ได้รับการออกแบบผ่าน IC ชิปตัวเดียว IC เหล่านี้เป็นส่วนประกอบที่ใช้งานได้จริงของระบบดิจิทัล หนึ่งในหน่วยการสร้างที่ใช้สําหรับการบวกไบนารีคือ Carry Look-ahead Adder

Carry Look-ahead Adder คืออะไร?

คอมพิวเตอร์ดิจิทัลต้องมีวงจรที่สามารถดําเนินการทางคณิตศาสตร์ เช่น การบวก การลบ การคูณ และการหาร ในบรรดาสิ่งเหล่านี้ การบวกและการลบเป็นการดําเนินการพื้นฐาน ในขณะที่การคูณและการหารคือการบวกและการลบซ้ําๆ ตามลําดับ

ในการดําเนินการเหล่านี้ 'วงจร Adder' จะถูกนําไปใช้โดยใช้ลอจิกเกตพื้นฐาน วงจร Adder ได้รับการพัฒนาเป็น Half-adder, Full-adder, Ripple-carry Adder และ Carry Look-ahead Adder

ในบรรดา Carry Look-ahead Adder เหล่านี้คือวงจรบวกที่เร็วกว่า ช่วยลดความล่าช้าในการแพร่กระจายซึ่งเกิดขึ้นระหว่างการเพิ่มโดยใช้วงจรฮาร์ดแวร์ที่ซับซ้อนมากขึ้น ได้รับการออกแบบโดยการแปลงวงจร Adder แบบกระเพื่อมเพื่อให้ตรรกะการพกพาของตัวเพิ่มเปลี่ยนเป็นตรรกะสองระดับ

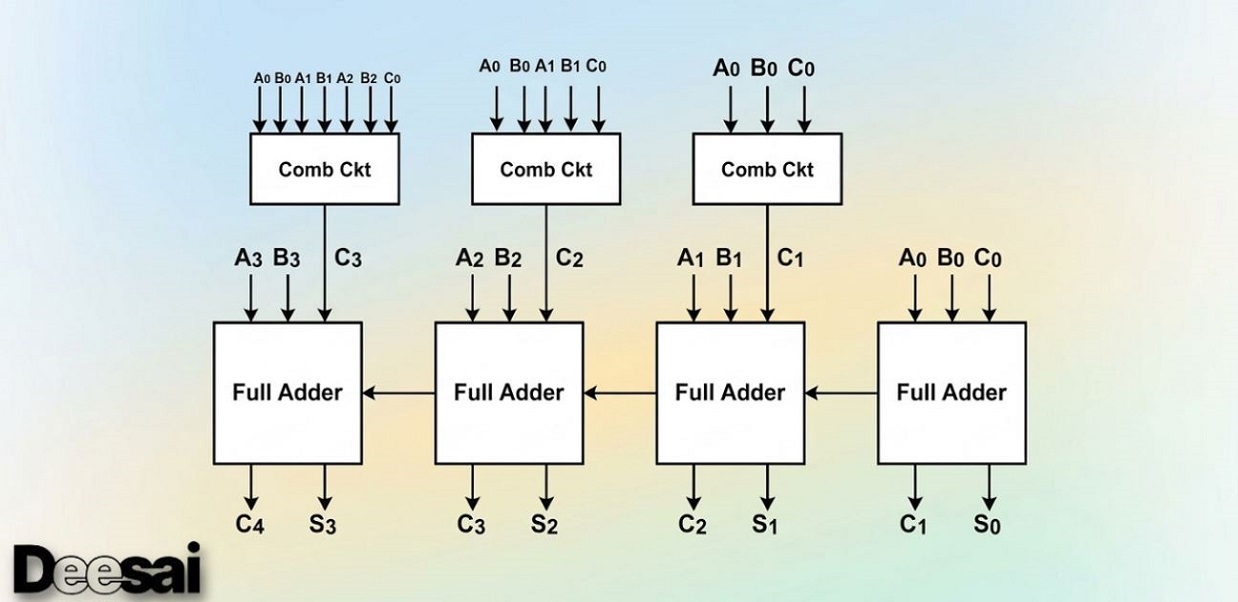

4-Bit Carry มองไปข้างหน้า Adder

ในการบวกแบบขนานเอาต์พุตการพกพาของตัวบวกเต็มแต่ละตัวจะได้รับเป็นอินพุตการพกพาไปยังสถานะลําดับที่สูงขึ้นถัดไป ดังนั้นตัวบวกเหล่านี้จึงเป็นไปไม่ได้ที่จะสร้างเอาต์พุตการพกพาและผลรวมของสถานะใด ๆ เว้นแต่จะมีอินพุตการพกพาสําหรับสถานะนั้น

ดังนั้นเพื่อให้การคํานวณเกิดขึ้นวงจรจะต้องรอจนกว่าบิตพกพาจะแพร่กระจายไปยังทุกสถานะ สิ่งนี้ทําให้เกิดความล่าช้าในการแพร่กระจายในวงจร

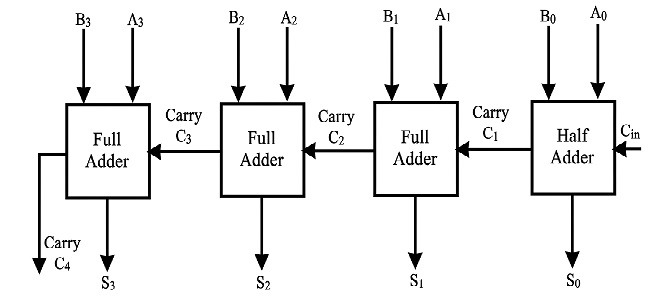

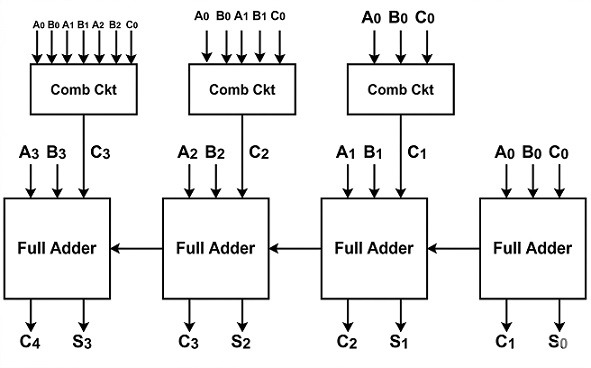

พิจารณาวงจร Ripple Carry Adder 4 บิตด้านบน ที่นี่สามารถสร้างผลรวม S3 ได้ทันทีที่ได้รับอินพุต A3 และ B3 แต่ไม่สามารถคํานวณ carry C3 ได้จนกว่าจะใช้ carry bit C2 ในขณะที่ C2 ขึ้นอยู่กับ C1 ดังนั้นเพื่อให้ได้ผลลัพธ์ในสภาวะคงที่ขั้นสุดท้าย carry จะต้องแพร่กระจายไปทั่วทุกสถานะ สิ่งนี้จะเพิ่มความล่าช้าในการแพร่กระจายของวงจร

ความล่าช้าในการแพร่กระจายของตัวบวกคํานวณเป็น "ความล่าช้าในการแพร่กระจายของแต่ละเกตคูณจํานวนขั้นตอนในวงจร" สําหรับการคํานวณบิตจํานวนมากจะต้องเพิ่มขั้นตอนเพิ่มเติมซึ่งทําให้ความล่าช้าแย่ลงมาก ดังนั้นเพื่อแก้ปัญหานี้จึงมีการแนะนํา Carry Look-ahead Adder

เพื่อให้เข้าใจการทํางานของ Carry Look-ahead Adder Carry Look-ahead Adder 4 บิตได้อธิบายไว้ด้านล่าง

ในตัวเพิ่มนี้ อินพุตการพกพาที่ขั้นตอนใด ๆ ของตัวเพิ่มจะไม่ขึ้นกับบิตการพกพาที่สร้างขึ้นในขั้นตอนอิสระ ที่นี่เอาต์พุตของขั้นตอนใด ๆ ขึ้นอยู่กับบิตที่เพิ่มเข้ามาในขั้นตอนก่อนหน้าและอินพุตการพกพาที่ให้ไว้ที่ขั้นตอนเริ่มต้นเท่านั้น ดังนั้นวงจรในทุกขั้นตอนจึงไม่ต้องรอการสร้าง carry-bit จากขั้นตอนก่อนหน้าและสามารถประเมิน carry bit ได้ตลอดเวลา

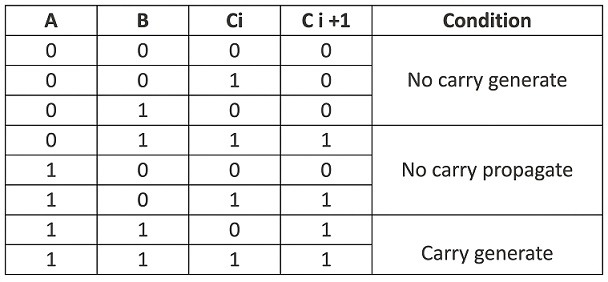

ตารางความจริงของ Carry Look-ahead Adder

สําหรับการได้มาซึ่งตารางความจริงของตัวบวกนี้ จะมีการแนะนําคําศัพท์ใหม่สองคํา – Carry generate และ carry propagate ดําเนินการสร้าง Gi =1 เมื่อใดก็ตามที่มีการสร้าง Ci+1 ขึ้นอยู่กับอินพุต Ai และ Bi Gi คือ 1 เมื่อทั้ง Ai และ Bi เป็น 1 ดังนั้น Gi จึงคํานวณเป็น Gi = Ai ไบ.

Carry propagated Pi เกี่ยวข้องกับการแพร่กระจายของ carry จาก Ci ไปยัง Ci+1 คํานวณเป็น Pi = Ai ⊕ Bi ตารางความจริงของตัวบวกนี้สามารถได้มาจากการแก้ไขตารางความจริงของตัวบวกแบบเต็ม

การใช้เงื่อนไข Gi และ Pi Sum Si และ Carry Ci+1 จะได้รับดังนี้ –

- ใช่ = Pi ⊕ Gi

- Ci+1 = Ci.Pi +กิ

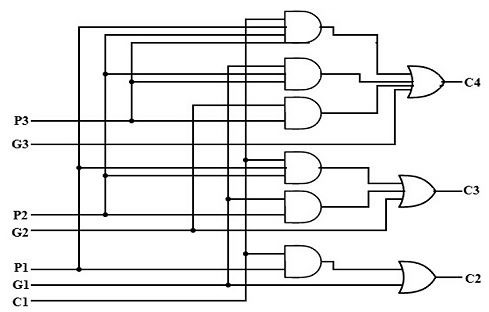

ดังนั้น carry bits C1, C2, C3 และ C4 สามารถคํานวณได้ดังนี้

- C1 = C0 P0+G0

- C2 = C1 P1+G1 = ( ค 0. P0+G0) P1+G1

- C3 = C2 P2+G2 = (ค 1. P1+G1) P2+G2

- C4 = C3 P3+G3 = C0 ป 0. ป.1. ป.2. หน้า 3 + หน้า 3 ป.2. ป.1. จี 0 + พี 3 ป.2. จี 1 + จี 2 หน้า 3 + ก 3

สามารถสังเกตได้จากสมการที่มี Ci+1 ขึ้นอยู่กับการพกพา C0 เท่านั้น ไม่ใช่บิตพกพาระดับกลาง

แผนภาพวงจร

สมการข้างต้นถูกนําไปใช้โดยใช้วงจรรวมสองระดับพร้อมกับเกต AND, OR โดยที่เกตจะถือว่ามีอินพุตหลายตัว

วงจร Carry Look-ahead Adder จาก 4 บิตแสดงไว้ด้านล่าง

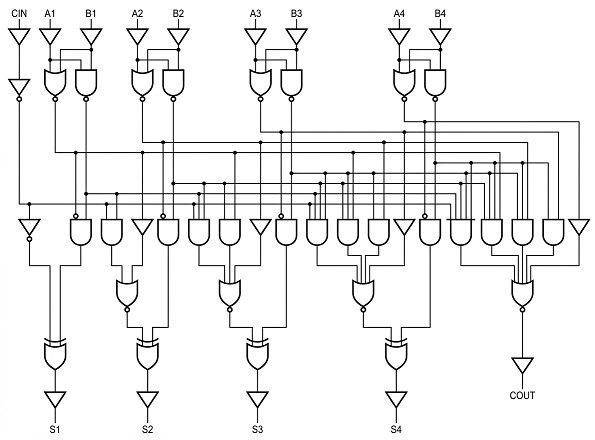

วงจร Carry Look-ahead Adder แบบ 8 บิตและ 16 บิตสามารถออกแบบได้โดยการเรียงซ้อนวงจร adder 4 บิตด้วยตรรกะการพกพา

ข้อดีของ Carry Look-ahead Adder

ในตัวเพิ่มนี้ความล่าช้าในการแพร่กระจายจะลดลง เอาต์พุตการพกพาในทุกขั้นตอนจะขึ้นอยู่กับบิตการพกพาเริ่มต้นของขั้นตอนเริ่มต้นเท่านั้น การใช้ตัวบวกนี้ทําให้สามารถคํานวณผลลัพธ์ระดับกลางได้ ตัวเพิ่มนี้เป็นตัวบวกที่เร็วที่สุดที่ใช้ในการคํานวณ

การใช้งาน

Carry Look-ahead Adders ความเร็วสูงถูกนํามาใช้เช่นเดียวกับ IC ดังนั้นจึงง่ายต่อการฝังตัวเพิ่มในวงจร ด้วยการรวมตัวบวกตั้งแต่สองตัวขึ้นไปการคํานวณของฟังก์ชันบูลีนบิตที่สูงขึ้นสามารถทําได้อย่างง่ายดาย ที่นี่การเพิ่มขึ้นของจํานวนเกตก็อยู่ในระดับปานกลางเมื่อใช้กับบิตที่สูงขึ้น

สําหรับ Adder นี้มีการแลกเปลี่ยนระหว่างพื้นที่และความเร็ว เมื่อใช้สําหรับการคํานวณบิตที่สูงขึ้นจะให้ความเร็วสูง แต่ความซับซ้อนของวงจรก็เพิ่มขึ้นเช่นกันซึ่งจะเพิ่มพื้นที่ที่วงจรครอบครอง ตัวเพิ่มนี้มักจะใช้เป็นโมดูล 4 บิตซึ่งเรียงซ้อนเข้าด้วยกันเมื่อใช้สําหรับการคํานวณที่สูงขึ้น แอดเดอร์นี้มีราคาแพงกว่าเมื่อเทียบกับแอดเดอร์อื่นๆ

สําหรับการคํานวณบูลีนในคอมพิวเตอร์มีการใช้แอดเดอร์เป็นประจํา Charles Babbage ใช้กลไกในการคาดการณ์บิตพกพาในคอมพิวเตอร์เพื่อลดความล่าช้าที่เกิดจากตัวเพิ่มการพกพาระลอกคลื่น ในขณะที่ออกแบบระบบความเร็วในการคํานวณเป็นปัจจัยในการตัดสินใจสูงสุดสําหรับนักออกแบบ ในปี 1957 Gerald B. Rosenberger ได้จดสิทธิบัตร Binary Carry Look-ahead Adder ที่ทันสมัย จากการวิเคราะห์ความล่าช้าของเกตและการจําลองกําลังดําเนินการทดลองเพื่อปรับเปลี่ยนวงจรของตัวเพิ่มนี้เพื่อให้เร็วยิ่งขึ้น สําหรับตัวบวกมองไปข้างหน้าแบบ n-bit ความล่าช้าในการแพร่กระจายคืออะไรเมื่อมีความล่าช้าของแต่ละเกตคือ 20

ผลิตภัณฑ์

March 25, 2026

Carry Look Ahead Adder – วงจรตารางความจริงและการใช้งาน

มาเรียนรู้ Carry-Lookahead Adder: วงจร ตารางความจริง และการใช้งานจริง

by

นักเขียนบทความ