ผลิตภัณฑ์

19

Jan

เข้าใจ ASIC: คู่มือฉบับสมบูรณ์สำหรับการใช้งาน IC ในการใช้งานเฉพาะทาง

Application-Specific Integrated Circuits (ASIC) คือชิปที่ออกแบบมาสำหรับการใช้งานเฉพาะทาง ทำให้มีประสิทธิภาพการทำงานที่เหมาะสมที่สุด

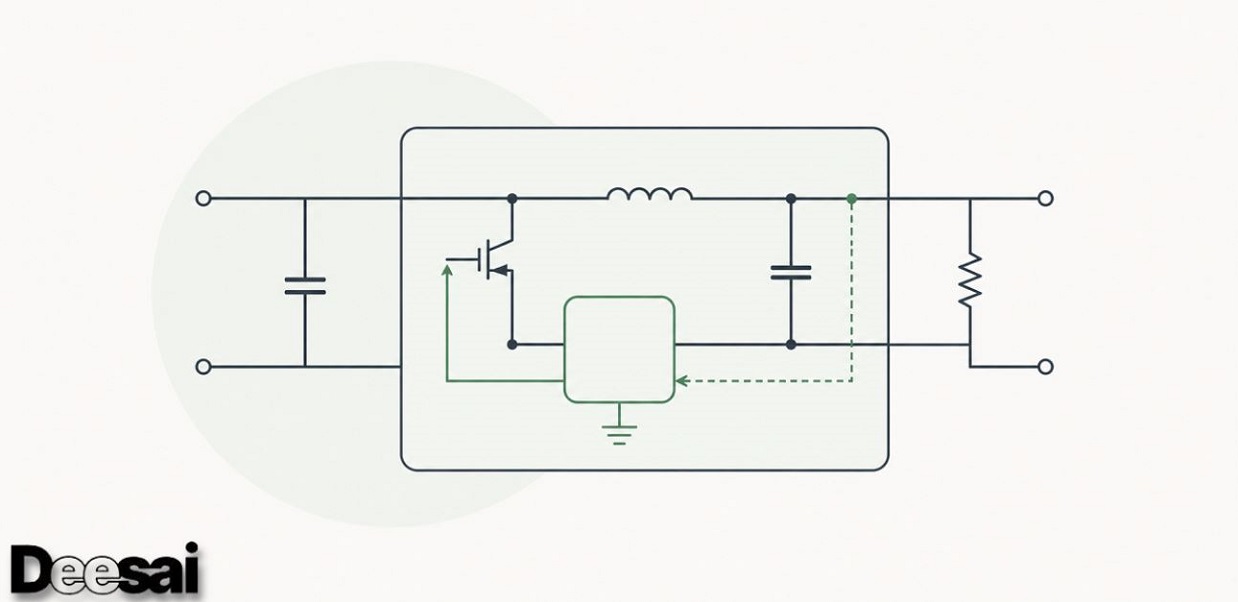

วงจรรวมสำหรับการใช้งานเฉพาะทาง (ASIC) คือวงจรรวม (IC) ที่ปรับแต่งให้เหมาะกับการใช้งานด้านใดด้านหนึ่งโดยเฉพาะ ไม่ได้ออกแบบมาเพื่อ การใช้งานทั่วไป ยกตัวอย่างเช่น ชิปที่ออกแบบมาสำหรับใช้งานในเครื่องบันทึกเสียงดิจิทัล (Digital Voice Recorder) หรือเครื่องขุด Bitcoin Mining ที่มีประสิทธิภาพสูง เนื่องจาก ASIC มีฟีเจอร์ขนาดเล็กลง และการออกแบบได้รับการพัฒนาขึ้นในช่วงหลายปีที่ผ่านมา ปัจจุบันจึงมีความซับซ้อนสูง ด้วยเหตุนี้จึงทำให้ฟังก์ชันการทำงานใน ASIC เพิ่มขึ้นจาก 5,000 เกต (GATE) เป็นมากกว่า 100 ล้านเกต อีกทั้ง ASIC จะประกอบไปด้วยไมโครโพรเซสเซอร์ ทั้งหมด ไม่ว่าจะเป็นหน่วยความจำ ROM, RAM, EEPROM, หน่วยความจำแฟลช และบล็อกการทำงานขนาดใหญ่อื่นๆ ASIC จึงมักถูกเรียกอีกอย่างนึงว่า “SoC” (ระบบบนชิป) ซึ่งนักออกแบบ ASIC มักใช้ภาษาอธิบายฮาร์ดแวร์ (HDL) Verilog หรือ VHDL เพื่ออธิบายฟังก์ชันการทำงานของ ASIC

ดังนั้น ASIC เป็นส่วนประกอบพื้นฐานที่จำเป็นสำหรับวงจรไฟฟ้าที่ใช้พลังงานสูง ทำให้ความหนาแน่นของช่องสัญญาณสูง เพิ่มประสิทธิภาพของสัญญาณแอนะล็อก (เช่น สัญญาณรบกวน ความเร็ว) ลดการสูญเสียพลังงาน ลดการเดินสาย ลดขนาด ลดต้นทุน และนำไปใช้งานด้านอื่นได้อีกเป็นจำนวนมาก อย่างไรก็ตาม ความต้องการ ASIC จะขึ้นอยู่กับการใช้งานเช่น การสุ่มตัวอย่างรูปคลื่นความเร็วสูง การจับเวลาที่รวดเร็ว การขยาย และการสร้างรูปร่างช่วงไดนามิกสูงที่มีสัญญาณรบกวนต่ำ การแปลงเป็นดิจิทัลความเร็วสูง การประมวลผลข้อมูลดิจิทัล การส่งข้อมูลอัตราสูง เช่นเดียวกับตัวอย่างด้านการใช้พลังงานเช่น การอัปเกรดความสว่างใน HL-LHC หรือ ASIC ต่ออุปกรณ์อิเล็กทรอนิกส์ในเครื่องตรวจจับ ซึ่งจะต้องมีการวิจัยและพัฒนาหลายด้านต่อไปในอนาคต

ประเภทของการออกแบบ ASIC

การออกแบบที่กำหนดเองทั้งหมด

รูปแบบการออกแบบที่กำหนดเองทั้งหมดเป็นแบบคลาสสิก ฟังก์ชันลอจิกดั้งเดิม หรือทรานซิสเตอร์แต่ละตัวจะได้รับการออกแบบและปรับให้เหมาะสมด้วยฝีมือ ทำให้การออกแบบชิปมีขนาดกะทัดรัดด้วยความเร็วสูงสุด และสูญเสียพลังงานน้อยที่สุด อย่างไรก็ตาม ต้นทุนในการลงทุนเริ่มต้น หรือวิศวกรรมแบบไม่เกิดขึ้นซ้ำ (NRE) จะสูงที่สุด เมื่อเทียบกับรูปแบบการออกแบบอื่นๆ ทั้งหมด นักออกแบบจะต้องจัดการรูปทรงแต่ละอัน ที่แสดงถึงคุณสมบัติของทรานซิสเตอร์แต่ละตัวบนชิป จึงมักใช้คำว่า “การผลักรูปหลายเหลี่ยม (Polygon Pushing)” สำหรับการออกแบบที่กำหนดเองทั้งหมด การออกแบบเกต 3,000 เกตที่ค่อนข้างเรียบง่ายอาจต้องจัดการสี่เหลี่ยมผืนผ้า 300,000 รูปต่อชิป แม้ว่ารูปแบบการออกแบบนี้จะใช้ใน IC ยุคแรกเท่านั้น แต่สำหรับวิศวกรในปัจจุบัน ไม่ค่อยได้ใช้รูปแบบนี้กับ ASIC เนื่องจากต้นทุนทางวิศวกรรมที่สูง และผลงานของนักออกแบบต่ำ ผลงานการออกแบบลอจิกที่กำหนดเองทั้งหมดโดยทั่วไปอยู่ที่ 6 ถึง 17 ทรานซิสเตอร์ต่อวันเท่านั้น ยกเว้นเรื่องที่เกี่ยวกับผลิตภัณฑ์โภคภัณฑ์ที่มีปริมาณมากเช่น หน่วยความจำ จำเป็นต้องทำด้วยมือเพื่อให้ตรงตามข้อกำหนดด้านความหนาแน่นและประสิทธิภาพ อีกทั้งผลิตภัณฑ์ระดับไฮเอนด์ส่วนน้อยบางส่วนเช่น ไมโครโปรเซสเซอร์ ออกแบบด้วยการกำหนดคุณสมบัติเองทั้งหมดด้วยเหตุผลด้านประสิทธิภาพ

การออกแบบ ASIC แบบเซลล์มาตรฐาน

ผู้ผลิต ASIC สร้างบล็อกฟังก์ชันที่ทำให้รู้คุณลักษณะทางไฟฟ้าเช่น ความล่าช้าของการแพร่กระจาย (Propagation Delay) ความจุ และความเหนี่ยวนำ เมื่อใช้บล็อคฟังก์ชันเหล่านี้ เซลล์มาตรฐานที่ได้รับการออกแบบจะมีความหนาแน่น ของเกตสูงมาก และมีประสิทธิภาพทางไฟฟ้าที่ดีทำให้มีความยืดหยุ่นสูง โดยต้องกำหนดให้เป็นไปตามข้อกำหนด ของฟังก์ชันมาตรฐาน ข้อได้เปรียบที่สำคัญของ ASIC แบบเซลล์มาตรฐานคือ ใช้ไลบรารีเซลล์ของผู้ผลิต ซึ่งเคยใช้ในการออกแบบมาแล้วหลายร้อยแบบ ดังนั้น ความเสี่ยงจึงต่ำมาก เมื่อเทียบกับการออกแบบแบบกำหนดเองทั้งหมด เซลล์มาตรฐานสร้างความหนาแน่นของการออกแบบที่คุ้มต้นทุน เวลาในการผลิตน้อย และยังสามารถผสานรวมคอร์ IP และ SRAM ได้อย่างมีประสิทธิภาพอีกด้วย

การออกแบบอาร์เรย์เกต

วิธีการออกแบบเซลล์แบบกำหนดเองและมาตรฐานทั้งหมดต้องใช้การผลิตชิปแบบกำหนด เอง โดยใช้ชุดมาสก์เฉพาะตัวที่สมบูรณ์ ซึ่งต้องกำหนดการประมวลผลในขั้นตอนการออกแบบ เซมิคอนดักเตอร์ ดังนั้นต้นทุน NRE สำหรับชุดมาสก์และเวลาในการออกแบบจึงค่อนข้างสูง ทางเลือกอีกทางคือ สร้างการออกแบบชิป โดยใช้รูปแบบการเชื่อมต่อแบบกำหนดเองบนอาร์เรย์ ของลอจิคเกตเช่น อาร์เรย์เกต เวเฟอร์ของชิปที่ยังไม่ได้กำหนดอาร์เรย์ลอจิคเกต แต่สามารถผลิตล่วงหน้าได้จนถึงขั้นตอนการ Metalizaion ขั้นสุดท้ายที่ปรับแต่งลอจิคได้ เมื่อเปรียบเทียบกับเซลล์มาตรฐาน หรือการออกแบบแบบกำหนดเองทั้งหมด เวลาในการออกแบบและต้นทุนจะลดลง เนื่องจากใช้ขั้นตอนการเชื่อมต่อและมาสก์แบบสัมผัส ข้อดีของอาร์เรย์เกต "โปรแกรมมาสก์" เกี่ยวข้องกับการประหยัด ขนาดพื้นที่สำหรับ รูปแบบการออกแบบ และต้นทุนเวเฟอร์ต่ำ เนื่องจากสามารถสร้างการออกแบบของลูกค้าที่แตกต่างกันได้หลายแบบ จากเวเฟอร์พื้นฐานแบบเดียวกัน ในทำนองเดียวกัน ต้นทุนการบรรจุภัณฑ์และการทดสอบจะต่ำลง เนื่องจากมีพินเอาต์มาตรฐาน และอุปกรณ์ทดสอบทั่วไปที่สามารถใช้กับการออกแบบได้หลายแบบ

การรออกแบบลอจิกที่สามารถตั้งโปรแกรมได้

อุปกรณ์ลอจิกที่ตั้งโปรแกรมได้คือ ชิปที่มีโครงสร้างลอจิกสุดท้าย ที่กำหนดค่าโดยตรง โดยผู้ใช้ปลายทาง เป็นการขจัดความจำเป็นในการทำวนซ้ำผ่านโรงงานผลิตวงจรรวม ทำให้เวลาในการออกสู่ตลาดและความเสี่ยงทางการเงินลดลงอย่างมาก ลอจิกที่ตั้งโปรแกรมได้มี 2 ประเภทหลักๆ ได้แก่ อุปกรณ์ลอจิกที่ตั้งโปรแกรมไว้ (PLD) และอาร์เรย์เกตที่ตั้งโปรแกรมไว้ (FPGA) ทั้งสองประเภทได้กลายเป็นโซลูชัน หรือคำตอบของ ASIC ที่คุ้มต้นทุน เนื่องจากมอบต้นแบบที่มีต้นทุนต่ำและเริ่มการผลิตได้ทันที อุปกรณ์ประเภทนี้ประกอบด้วยอาร์เรย์ขององค์ประกอบลอจิกที่ไม่ได้กำหนดค่าไว้ ซึ่งโครงสร้างการเชื่อมต่อ หรือโครงสร้างลอจิกสามารถปรับแต่งได้ตามข้อกำหนดของผู้ใช้

ความได้เปรียบของ ASIC

- ขนาดเล็ก ASIC ได้รับการออกแบบด้วยการวางผังขนาดพื้นที่ให้เหมาะสม ดังนั้นขนาดของ ASIC ที่ออกแบบมาสำหรับการใช้งานเฉพาะทางจึงมีขนาดเล็กกว่า เมื่อเทียบกับอุปกรณ์ที่ตั้งโปรแกรมได้อื่นๆ ด้วยเหตุนี้ ขนาดที่เล็กของ ASIC จึงนำไปสู่ข้อได้เปรียบด้านความเร็วและการใช้พลังงาน

- ไม่มีปัญหาด้านการกำหนดเส้นทางหรือการเดินสาย ไม่มีปัญหาใดๆ เกี่ยวกับการกำหนดเส้นทางปลายทางต่อการใช้งานใน ASIC เมื่อได้รับการออกแบบแล้ว

- ไม่มีปัญหาเรื่องเวลา การสลับลอจิกดิจิทัล เอฟเฟกต์ของแอนะล็อก และการสื่อสารระหว่างบล็อกในชิปจะเร็วกว่าใน ASIC ฮาร์ดแวร์ที่กำหนดค่าได้ จะต้องตรงตามข้อกำหนดด้านเวลา เพื่อให้วงจรทำงานอย่างมีประสิทธิภาพ สายไฟที่ยาวขึ้นระหว่างส่วนประกอบอาจส่งผลต่อเวลา บางครั้ง การออกแบบใหม่ที่เพิ่มเข้ามา อาจส่งผลให้เกิดผลลัพธ์ที่ผิดพลาดหากเกินเวลาหรือต่ำกว่าเวลาที่กำหนด แต่ ASIC ไม่มีปัญหานี้

- ใช้พลังงานน้อยลง ASIC ใช้พลังงานน้อยลงจากการทำงานของลอจิกเกิดขึ้นภายในชิป เนื่องจากส่วนประกอบที่มีขนาดเล็กกว่าจะมีความต้านทาน ความจุ และความเหนี่ยวนำน้อยกว่ามาก

- ความสม่ำเสมอและความน่าเชื่อถือ ASIC มีประสิทธิภาพการทำงานที่สม่ำเสมอและเชื่อถือได้ เนื่องจากได้รับการออกแบบโดยนักออกแบบที่มีทักษะเพื่อทำงานเฉพาะทางอย่างเดียว นอกจากนี้ โอกาสที่วงจรรวมจะล้มเหลวและได้รับผลกระทบจากสภาพแวดล้อมภายนอกมีน้อย ทำให้อายุการใช้งานของ ASIC ยาวนานขึ้นมาก เนื่องจากใช้ IC เป็นพื้นฐาน

ผลิตภัณฑ์

April 23, 2025

เข้าใจ ASIC: คู่มือฉบับสมบูรณ์สำหรับการใช้งาน IC ในการใช้งานเฉพาะทาง

Application-Specific Integrated Circuits (ASIC) คือชิปที่ออกแบบมาสำหรับการใช้งานเฉพาะทาง ทำให้มีประสิทธิภาพการทำงานที่เหมาะสมที่สุด

by

นักเขียนบทความ