ผลิตภัณฑ์

19

Jan

JK Flip-Flop (บทช่วยสอนเริ่มต้นอย่างรวดเร็ว)

ในบทช่วยสอนนี้ คุณจะได้เรียนรู้วิธีการทํางาน ตารางความจริง และวิธีสร้างด้วยลอจิกเกต

JK Flip-Flop เป็นฟลิปฟล็อปประเภทหนึ่งที่สามารถตั้งค่า รีเซ็ต และสลับได้ สามารถใช้สําหรับทําเคาน์เตอร์ เครื่องตรวจจับเหตุการณ์ ตัวแบ่งความถี่ และอื่นๆ อีกมากมาย

ในบทช่วยสอนนี้ คุณจะได้เรียนรู้วิธีการทํางาน ตารางความจริง และวิธีสร้างด้วยลอจิกเกต

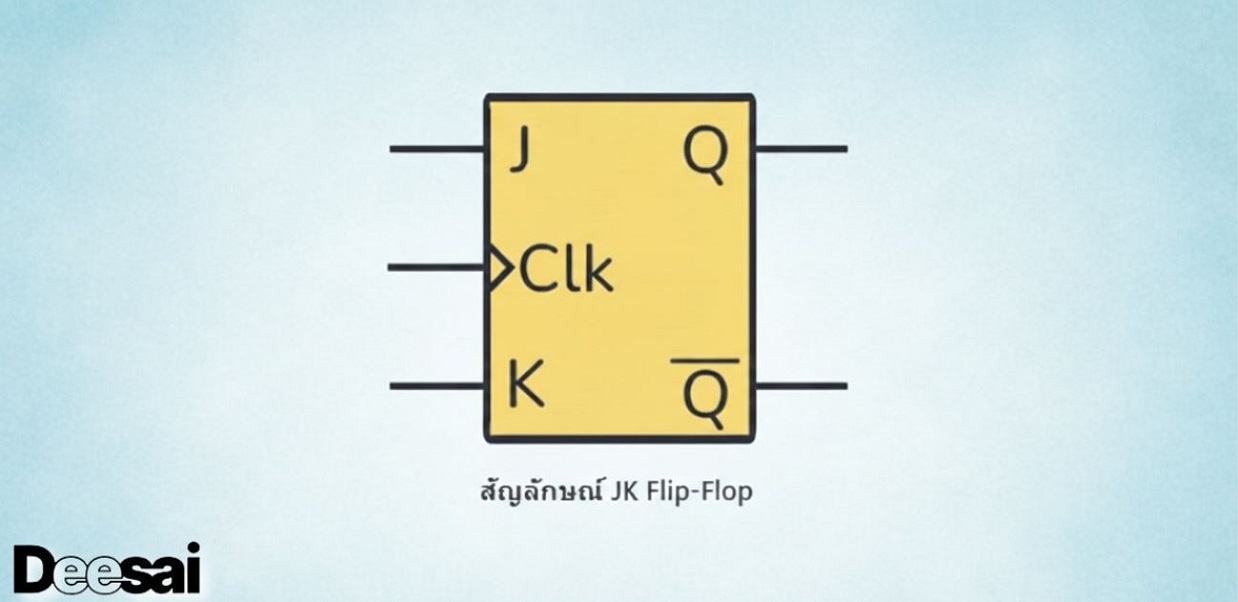

JK Flip-Flop คืออะไร?

รองเท้าแตะเป็นส่วนประกอบที่สามารถจัดเก็บค่าดิจิทัลบนเอาต์พุตได้ พวกเขามีอินพุตนาฬิกา (Clk) ซึ่งกําหนดว่าเมื่อใดที่สามารถเปลี่ยนสถานะของเอาต์พุตได้

ตรงกันข้ามกับสิ่งที่คุณคิดอินพุตสองตัวของ JK Flip-Flop "J" และ "K" ไม่ใช่ตัวย่อสําหรับสิ่งที่หมุดทํา (ซึ่งเป็นกรณีของสลัก SR) พวกเขาได้รับเลือกจากนักประดิษฐ์ Jack Kilby (JK) เพื่อแยกความแตกต่างระหว่างการออกแบบรองเท้าแตะของเขาจากประเภทอื่นๆ

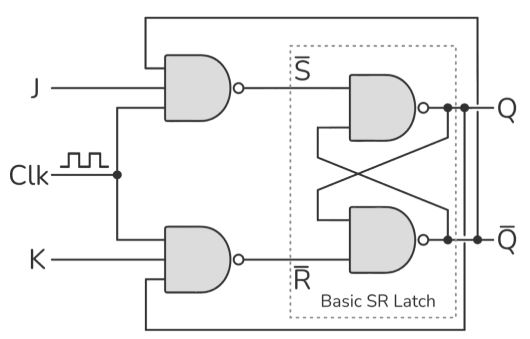

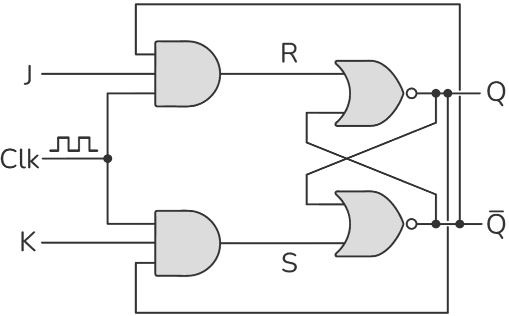

คุณสามารถดูการใช้งานพื้นฐานของวงจรด้านล่าง มันขึ้นอยู่กับสลัก SR และสร้างขึ้นด้วยเกต NAND:

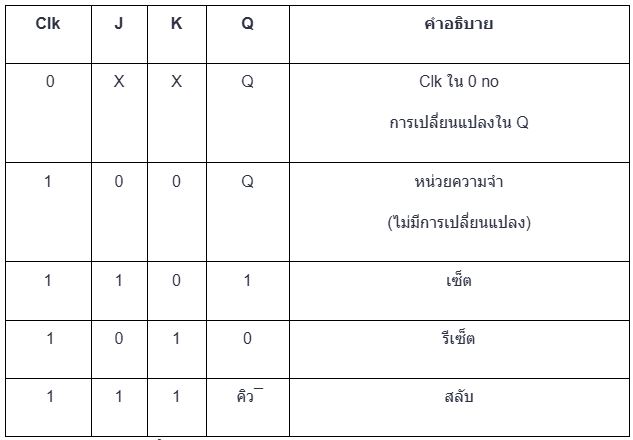

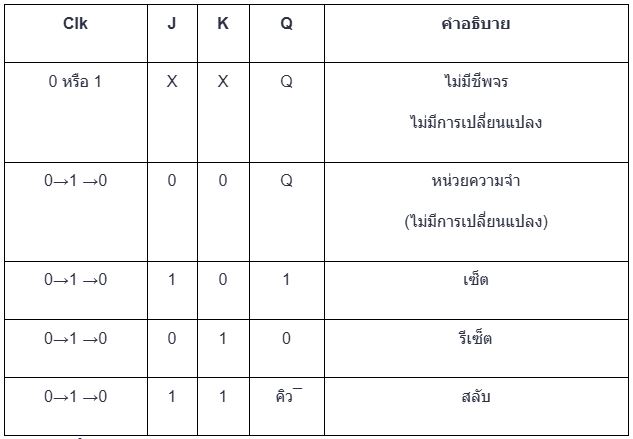

อินพุต J และ K ของฟลิปฟล็อป JK สามารถใช้เพื่อตั้งค่า รีเซ็ต หรือสลับเอาต์พุตได้ดังนี้:

- J=1 และ K=0 ตั้งค่าเอาต์พุตเป็น 1

- J=0 และ K=1 รีเซ็ตเอาต์พุตเป็น 0

- J=1 และ K=1 สลับเอาต์พุต

แต่เพื่อให้ฟลิปฟล็อปทําการเปลี่ยนแปลงใด ๆ อินพุตนาฬิกาจะต้องเป็น 1 ตรวจสอบตารางความจริงด้านล่าง:

อีกวิธีหนึ่งในการใช้วงจรฟลิปฟล็อป JK พื้นฐานคือการใช้เกต AND สองเกตและเกต NOR สองเกตดังนี้ (ทํางานเหมือนกับที่สร้างด้วยเกต NAND):

ปัญหาการแข่งรถ

โดยหลักการแล้วการใช้งานพื้นฐานข้างต้นใช้งานได้ แต่มีปัญหาเรื่องเวลาเกิดขึ้น เมื่อนาฬิกาเป็น "1" และคุณต้องการสลับเอาต์พุต นาฬิกาจะสลับอย่างรวดเร็วระหว่าง "1" และ "0" จนกว่านาฬิกาจะกลับไปที่ "0" ปัญหานี้เรียกว่าสภาวะการแข่งขัน

คุณสามารถแก้ปัญหานี้ได้โดยทําให้ฟลิปฟล็อปเป็นพัลส์ทริกเกอร์หรือทริกเกอร์ขอบ

JK Flip-Flop ที่ทริกเกอร์ด้วยพัลส์

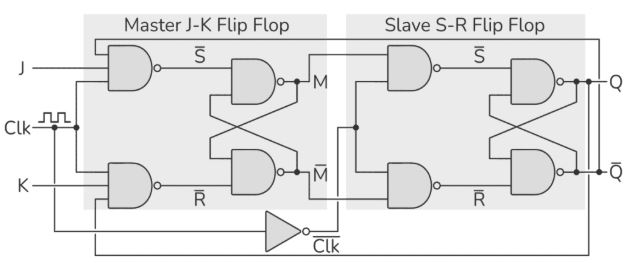

ด้านล่างนี้คุณมีฟลิปฟล็อป JK ที่ทริกเกอร์ด้วยพัลส์ตามหลักการ Master-Slave:

อย่างที่คุณเห็นในการสร้างการกําหนดค่านี้คุณต้องมีวงจร JK Flip-Flop พื้นฐานที่ผูกติดกับฟลิปฟล็อป SR

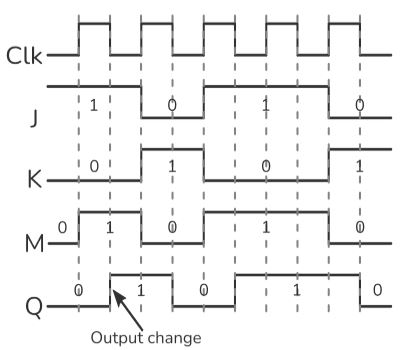

หากต้องการทําความเข้าใจว่าเวอร์ชันนี้ทํางานอย่างไร โปรดดูแผนภาพเวลาด้านล่าง:

ทันทีที่นาฬิกาทําขอบเพิ่มขึ้น↑ ซึ่งเป็นการเปลี่ยนแปลงจาก 0 เป็น 1 (0→1) นาฬิกาจะทริกเกอร์ส่วนหลัก ด้วยเหตุนี้ ค่าของผลลัพธ์ในส่วนนี้จึงเปลี่ยนไป สัญญาณเหล่านี้เชื่อมต่อกับส่วนทาส แต่สิ่งนี้จะไม่ทริกเกอร์ที่ขอบที่เพิ่มขึ้นเนื่องจากนาฬิกากลับด้าน

เมื่อสัญญาณนาฬิกาสร้างขอบที่ลดลง ↓ การเปลี่ยนแปลงจาก 1 เป็น 0 (1→0) มันจะทริกเกอร์ส่วนรอง ทําให้เอาต์พุต Q สะท้อนถึงค่าเอาต์พุตของต้นแบบ

ดังนั้นวงจรนี้จึงต้องใช้พัลส์ที่สมบูรณ์ (0→1 →0) เพื่อเปลี่ยนเอาต์พุต นั่นเป็นเหตุผลที่การกําหนดค่านี้เรียกว่า JK Flip-Flop ที่ทริกเกอร์ด้วยพัลส์

JK Flip-Flop ที่ทริกเกอร์ขอบ

ซึ่งแตกต่างจากการออกแบบ Master-Slave ที่ต้องการพัลส์ที่สมบูรณ์ คุณยังสามารถสร้างการออกแบบที่ทริกเกอร์ขอบที่ทริกเกอร์จากขอบที่เพิ่มขึ้น ↑ หรือขอบที่ลดลง ↓

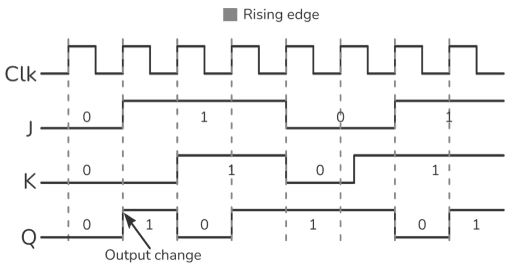

ด้านล่างนี้คุณมีแผนภาพเวลาสําหรับไดอะแกรมที่ทริกเกอร์ที่ขอบที่เพิ่มขึ้น:

ภาพด้านบนแสดงให้เห็นว่าวงจรนี้ต้องการขอบที่เพิ่มขึ้นบนอินพุต Clk เพื่อเปลี่ยนสถานะของเอาต์พุต Q ได้อย่างไร และมันจะเปลี่ยนไปบนขอบที่เพิ่มขึ้นเท่านั้น

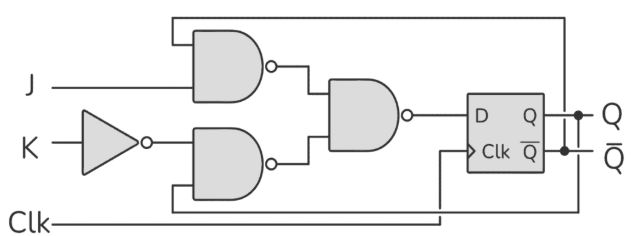

ในการสร้าง JK Flip-Flop ที่ทริกเกอร์เฉพาะกับสัญญาณขอบที่เพิ่มขึ้นคุณสามารถใช้ฟลิปฟล็อป D ที่ทริกเกอร์ขอบที่เพิ่มขึ้นเกต NOT และเกต NAND ดังนี้:

วงจรรวมพร้อม JK Flip-Flop

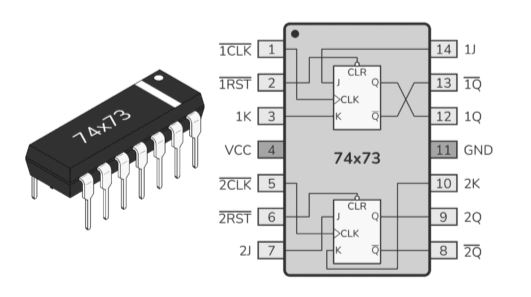

ต้องการรองเท้าแตะ JK หรือไม่? คุณไม่จําเป็นต้องสร้างมันขึ้นมาตั้งแต่เริ่มต้น มีวงจรรวมจํานวนมากที่มีวงจร JK Flip-Flop อยู่ภายใน สองตัวเลือกทั่วไปคือชิป CD4027 หรือ 74HC73 IC

ผลิตภัณฑ์

February 11, 2026

JK Flip-Flop (บทช่วยสอนเริ่มต้นอย่างรวดเร็ว)

ในบทช่วยสอนนี้ คุณจะได้เรียนรู้วิธีการทํางาน ตารางความจริง และวิธีสร้างด้วยลอจิกเกต

by

นักเขียนบทความ