ผลิตภัณฑ์

19

Jan

การออกแบบระดับการถ่ายโอนทะเบียน (RTL) คืออะไร?

การออกแบบระดับการถ่ายโอนรีจิสเตอร์ (RTL) เป็นวิธีการอธิบายวิธีการเคลื่อนย้ายและประมวลผลข้อมูลระหว่างรีจิสเตอร์ในวงจรดิจิทัล

การออกแบบระดับรีจิสเตอร์ (RTL) เป็นขั้นตอนสำคัญในกระบวนการออกแบบวงจรดิจิทัล การกำหนดและปรับแต่งฟังก์ชันลอจิกของการออกแบบดิจิทัลในระดับนามธรรมก่อนการกำหนดโครงร่างทางกายภาพของวงจร วิศวกรจะแปลงพฤติกรรมที่ต้องการระดับสูงของการออกแบบเป็นโค้ดซอฟต์แวร์โดยใช้ภาษาอธิบายฮาร์ดแวร์ (HDL) เช่น VHDL หรือ Verilog

HDL ตัวแรกที่สามารถสร้างแบบจำลองในระดับ RTL ได้รับการพัฒนาในช่วงทศวรรษ 1980 และพัฒนาไปเป็นระบบการออกแบบเต็มรูปแบบที่ช่วยให้วิศวกรสามารถสร้างแบบจำลองการไหลของข้อมูลในวงจรอิเล็กทรอนิกส์ได้

เมื่อการออกแบบมีขนาดใหญ่ขึ้นและซับซ้อนขึ้น และเทคโนโลยีการผลิตก็เปิดโอกาสให้มีวิธีการใหม่ๆ ในการนำตรรกะและการคำนวณทางคณิตศาสตร์มาใช้ วิธีการออกแบบ RTL จึงได้รับความนิยม เมื่อเวลาผ่านไป การออกแบบ RTL กลายเป็นขั้นตอนสำคัญในกระบวนการออกแบบดิจิทัล โดยเชื่อมโยงขั้นตอนการออกแบบระบบและการออกแบบวงจรเข้าด้วยกัน

ลักษณะนามธรรมของคำอธิบาย RTL ช่วยให้สามารถศึกษาและออกแบบซ้ำได้อย่างรวดเร็วเพื่อให้ได้การออกแบบที่เหมาะสมที่สุดและเป็นที่ยอมรับ ก่อนที่จะเจาะลึกเข้าสู่ขั้นตอนที่ซับซ้อนและใช้เวลานานมากขึ้นในกระบวนการออกแบบ

การออกแบบ RTL เป็นส่วนสำคัญของวงจรการออกแบบวงจรรวม ช่วยให้วิศวกรสามารถเพิ่มประสิทธิภาพการออกแบบได้ตั้งแต่ขั้นตอนรีจิสเตอร์ ตัวดำเนินการ และการไหลของข้อมูล ก่อนที่จะต้องกังวลเกี่ยวกับส่วนประกอบทางกายภาพและวิธีการเชื่อมต่อ ในบทความนี้ เราจะครอบคลุมหลักการพื้นฐานบางประการ อธิบายบทบาทของการออกแบบ RTL ในการออกแบบวงจรดิจิทัล และอธิบายกระบวนการออกแบบ RTL จากนั้นเราจะแสดงให้เห็นว่าการออกแบบ RTL สอดคล้องกับการออกแบบชิปวงจรรวมแบบ Field-Programmable Gate Array (FPGA) และวงจรรวมเฉพาะแอปพลิเคชัน (ASIC) อย่างไร และเผยให้เห็นอนาคตของการออกแบบ RTL

หลักการพื้นฐานของการออกแบบ RTL

วลี "register-transfer" หมายถึงวิธีที่ภาษาอธิบายการไหลของข้อมูลระหว่างรีจิสเตอร์ และวิธีการใช้ตรรกะและการดำเนินการทางคณิตศาสตร์กับข้อมูล วิศวกรใช้การออกแบบ RTL เพื่ออธิบายบล็อกฟังก์ชัน ซึ่งกำหนดพฤติกรรมของส่วนประกอบแยกส่วนที่ใช้ในการทำงานเฉพาะ บล็อกฟังก์ชันแต่ละบล็อกมีคำอธิบายของรีจิสเตอร์ภายในบล็อก ซึ่งเรียกว่าวงจรลำดับ และวงจรเชิงผสมที่ประกอบด้วยการดำเนินการเชิงตรรกะสำหรับบล็อกฟังก์ชันนั้น พวกเขายังใช้ HDL เพื่ออธิบายวิธีการเชื่อมต่อบล็อกฟังก์ชันเพื่อกำหนดการไหลของข้อมูลผ่านวงจร

พลังของการออกแบบ RTL อยู่ที่วิธีการแบ่งระบบที่ซับซ้อนออกเป็นบล็อกที่ค่อนข้างเรียบง่าย ซึ่งแสดงด้วยโค้ด HDL ต่อไปนี้คือพื้นฐานสำคัญบางประการเพื่อทำความเข้าใจวิธีใช้การออกแบบ RTL

ลงทะเบียน

ในการออกแบบ RTL ส่วนประกอบฮาร์ดแวร์ที่สามารถเก็บข้อมูลจำนวนหนึ่งเรียกว่ารีจิสเตอร์ ซึ่งโดยปกติแล้วจะใช้เป็นฟลิปฟล็อป D ค่าของรีจิสเตอร์สามารถอ่านเป็นอินพุตของการดำเนินการทางตรรกะ หรือสามารถตั้งค่าเป็นเอาต์พุตของการดำเนินการได้ วัตถุประสงค์พื้นฐานของการออกแบบ RTL คือการอธิบายวิธีการไหลของข้อมูลระหว่างรีจิสเตอร์และวิธีการเปลี่ยนแปลงข้อมูลโดยการดำเนินการ

ภาษาคำอธิบายฮาร์ดแวร์ (HDL)

ส่วนที่สำคัญที่สุดของการออกแบบ RTL คือโค้ดที่อธิบายพฤติกรรมของวงจร HDL เป็นภาษาสเปกที่มีลักษณะคล้ายกับภาษาโปรแกรมมาก โดยมีตัวแปร การเรียกใช้ฟังก์ชัน คำสั่งตรรกะ เช่น if-then-else และ CASE คำสั่งบูลีน และคณิตศาสตร์ อย่างไรก็ตาม HDL ได้รับการออกแบบมาโดยเฉพาะเพื่ออธิบายพฤติกรรมและโครงสร้างของวงจรอิเล็กทรอนิกส์ ซึ่งโดยปกติแล้วจะเป็นวงจรรวม ความแตกต่างอย่างหนึ่งระหว่าง HDL และภาษาโปรแกรมคือ แนวคิดเรื่องเวลาถูกสร้างไว้ในภาษา เพื่อให้การทำงานสามารถถูกเรียกใช้งานโดยนาฬิกาในวงจรได้

การดำเนินการนี้ทำได้โดยใช้ตัวแปรที่กำหนดค่าของนาฬิกาดิจิทัลในวงจร เช่นในตัวอย่างง่ายๆ ของอินเวอร์เตอร์ VHDL นี้ โดยที่เอาต์พุต (Q) จะถูกตั้งเป็นค่าอินพุต (D) เมื่อค่านาฬิกา clk เปลี่ยนจากสถานะต่ำไปเป็นสถานะสูง (ขอบขึ้น):

D <= not Q;

process(clk)

begin

if rising_edge(clk) then

Q <= D;

end if;

end process;HDL หรือ Very High Speed Integrated Circuit Hardware Description Language (VHDL) ที่ใช้กันอย่างแพร่หลายที่สุด เป็นภาษาที่มีรูปแบบซับซ้อนและมีการพิมพ์ที่เข้มงวด โดยมีไวยากรณ์ที่แตกต่างจากภาษา C ถือเป็น HDL ที่นิยมใช้สำหรับการอธิบายการออกแบบระบบที่ซับซ้อนมากขึ้น

HDL อีกตัวหนึ่งที่ได้รับความนิยมคือ Verilog หรือ SystemVerilog ซึ่งเป็นซูเปอร์เซ็ตของ Verilog Verilog มีขนาดสั้นกว่า มีชนิดข้อมูลน้อยกว่า มีความยืดหยุ่นมากกว่า และมีไวยากรณ์คล้ายกับโค้ดภาษา C เนื่องจาก Verilog เรียนรู้และเขียนคำอธิบายได้ง่าย วิศวกรจึงมักใช้ Verilog เมื่อเริ่มต้นใช้งานหรือเมื่อวงจรไม่ซับซ้อนเกินไป IEEE กำหนดทั้ง Verilog และ VHDL ให้เป็นมาตรฐานอุตสาหกรรม

นี่คือตัวอย่างง่ายๆ ของเกต AND ในทั้งสองภาษา เกต AND มีอินพุตสองอินพุตและเอาต์พุตหนึ่งเอาต์พุต หากอินพุตทั้งสองเป็น 1 เอาต์พุตจะเป็น 1 หากอินพุตทั้งสองไม่เท่ากันหรือตั้งค่าเป็น 0 เอาต์พุตจะเป็น 0

VHDL อธิบายเกต AND ดังต่อไปนี้:

entity my_and is -- First, you define the entity

port (

inp1: in std_logic; -- The first port

inp2: in std_logic; -- The second port

rst: out std_logic -- The output port

);

end my_and;

architecture blk of my_and is -- Next, define the architecture

begin

process(inp1, inp2) -- With the inputs, do the following

Begin

-- Use a simple if-then-else statement

if((inp1=’1’) and inp1=’1’))then

rst <= ’1’;

else

rst <= ’0’;

End if;

end process

end blk;Verilog สำหรับ AND gate มีลักษณะดังนี้:

module my_and(inp1,inp2,rst); // define the module call

input inp1, inp2; // define inputs and output

output rst;

assign rst = inp1 & inp2; // use the & (and) operator

endmoduleตรรกะนี้รับค่าที่พอร์ตอินพุตสองพอร์ต และตั้งค่าเอาต์พุตเป็น 1 หากทั้งสองพอร์ตมีค่าเป็น 1 นี่เป็นเพียงตัวอย่างง่ายๆ แต่โค้ดประเภทนี้สามารถแทนเอนทิตีใดๆ ก็ได้ในระบบ และสามารถนำมารวมกันเพื่อกำหนดวงจรดิจิทัลทั้งหมดได้ ส่วนประกอบพื้นฐานทั่วไปประกอบด้วยตัวบวก ตัวคูณ ตัวนับ หน่วยความจำ และสเตตแมชชีน เมื่อวิศวกรออกแบบกำหนดระบบแล้ว โค้ดจะถูกส่งไปยังคอมไพเลอร์ หากคอมไพเลอร์ทำงานได้โดยไม่มีข้อผิดพลาด วิศวกรสามารถใช้ผลลัพธ์ที่ได้เพื่อทดสอบระบบได้

การดำเนินการเชิงตรรกะ

ในการออกแบบ RTL มีสองประเภท ประเภทแรกคือการดำเนินการทางตรรกะ ซึ่งจะประเมินและแก้ไขข้อมูลแต่ละบิตที่เก็บไว้ในรีจิสเตอร์ การดำเนินการทางตรรกะ เช่น AND, OR, NOT, XOR และ shift ถูกสร้างขึ้นโดยการกำหนดพฤติกรรมทางตรรกะใน HDL ตัวอย่างข้างต้นแสดงวิธีการแสดง AND ใน VHDL และ Verilog การดำเนินการทางตรรกะจะแสดงเกตทางตรรกะในฮาร์ดแวร์

การดำเนินการทางคณิตศาสตร์

การดำเนินการประเภทที่สองในการออกแบบ RTL คือการดำเนินการทางคณิตศาสตร์ การดำเนินการเหล่านี้จะนำข้อมูลจากรีจิสเตอร์มาบวก ลบ คูณ และหาร การดำเนินการเหล่านี้แสดงใน HDL โดยใช้ตัวดำเนินการทางคณิตศาสตร์มาตรฐาน ตัวอย่างเช่น การบวกเลขสองจำนวนใน VHDL จะใช้คำสั่งต่อไปนี้:

rst <= inp1 + inp2;— โดยที่ inp1 และ inp2 เป็นรีจิสเตอร์อินพุตสองตัว และ rst ถูกกำหนดให้กับรีจิสเตอร์เอาต์พุต การดำเนินการทางคณิตศาสตร์ใน RTL แสดงถึงองค์ประกอบทางกายภาพเฉพาะ เช่น ตัวบวก ตัวลบ ตัวคูณ และตัวหาร

การดำเนินการแบบซิงโครนัสและอะซิงโครนัส

การออกแบบ RTL สามารถแสดงการไหลของข้อมูลได้ทั้งแบบซิงโครนัสและอะซิงโครนัส ในแบบซิงโครนัส ซับรูทีนจะถูกดำเนินการหรือทริกเกอร์โดยอินพุตสัญญาณนาฬิกาของระบบที่ส่งไปยังฟังก์ชัน ในแบบอะซิงโครนัส ซับรูทีนจะถูกดำเนินการเมื่อค่าของพอร์ตอินพุตหนึ่งพอร์ตหรือมากกว่าเปลี่ยนแปลงไปในลักษณะเฉพาะ ซึ่งทำได้โดยการตรวจสอบค่าอินพุตของอินพุตสัญญาณนาฬิกาหรืออินพุตที่ไม่ใช่สัญญาณนาฬิกา เพื่อดูว่ามีการเปลี่ยนแปลงหรือไม่โดยใช้คำสั่ง if

บทบาทของ RTL ในการออกแบบวงจรรวม

กระบวนการออกแบบวงจรรวม (IC) สมัยใหม่เกี่ยวข้องกับการนำข้อกำหนดว่าอุปกรณ์ต้องทำอะไรมาแปลงเป็นชิปเซมิคอนดักเตอร์แบบแพ็กเกจ ระดับของการแยกส่วนที่การออกแบบ RTL มอบให้ ช่วยให้วิศวกรสามารถมุ่งเน้นไปที่ฟังก์ชันระดับสูงของระบบได้โดยไม่ต้องพิจารณารายละเอียดเฉพาะเจาะจงว่าการออกแบบนั้นถูกนำไปใช้งานจริงอย่างไร

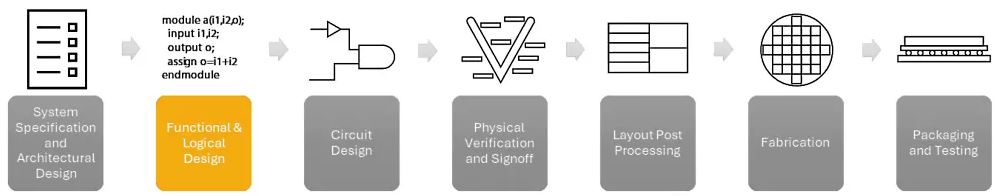

ขั้นตอนแรกในกระบวนการออกแบบวงจรรวม (IC) คือการกำหนดรายละเอียดระบบและการออกแบบสถาปัตยกรรม ข้อมูลนี้จะถูกแปลงเป็นรหัส HDL จากนั้นวิศวกรจะใช้รหัสนั้นเพื่อกำหนดการออกแบบเชิงฟังก์ชันและเชิงตรรกะ เมื่อการออกแบบเสร็จสมบูรณ์ การออกแบบจะถูกแปลงเป็นเน็ตลิสต์ ซึ่งจะถูกนำไปใช้ในการสร้างการออกแบบวงจร และดำเนินการกับกระบวนการออกแบบที่เหลือต่อไป

การนำเสนอแบบร่างของ RTL จะต้องดำเนินการให้เร็วที่สุดเท่าที่จะเป็นไปได้ในกระบวนการออกแบบ ก่อนที่จะลงทุนทั้งเวลาและเงินไปกับการออกแบบทางกายภาพ การตรวจสอบการออกแบบทางกายภาพ หรือการผลิตฮาร์ดแวร์จริง การรวมขั้นตอนการออกแบบ RTL เข้ากับกระบวนการนี้จำเป็นต้องอาศัยการผสานรวมที่ดีระหว่างข้อกำหนดระบบเบื้องต้นและเครื่องมืออันทรงพลังที่แปลงรีจิสเตอร์ การดำเนินการ และกระแสข้อมูลให้เป็นวงจรจริงเมื่อการออกแบบ RTL เสร็จสมบูรณ์

การออกแบบ RTL

เป้าหมายของขั้นตอนการออกแบบ RTL คือการกำหนดและเพิ่มประสิทธิภาพการทำงานของวงจรรวม ซึ่งโดยทั่วไปคือ FPGA หรือ ASIC วิศวกรออกแบบใช้ขั้นตอนการออกแบบ RTL เพื่อกำหนดตรรกะและขั้นตอนการทำงานของอุปกรณ์สำหรับการทดสอบและเพิ่มประสิทธิภาพระบบก่อน จากนั้นจึงแปลงนิยาม RTL ให้เป็นเน็ตลิสต์ ห้าขั้นตอนต่อไปนี้จะกำหนดแนวทางการออกแบบ RTL ทั่วไป

1. สรุประดับสูง

งานแรกของกระบวนการคือการแปลงข้อมูลจำเพาะของอุปกรณ์เป็นโค้ด HDL โดยมีการปรับเปลี่ยนให้น้อยที่สุด ในกรณีส่วนใหญ่ วิศวกรจะแสดงพฤติกรรมของอุปกรณ์ที่ต้องการในภาษาโปรแกรมมาตรฐาน เช่น C หรือ C++ จากนั้นเครื่องมือซอฟต์แวร์จะวิเคราะห์อัลกอริทึมในแบบจำลองซอฟต์แวร์เป็นภาษาข้อมูลจำเพาะที่เลือกไว้ ขั้นตอนนี้สามารถข้ามได้สำหรับการออกแบบที่เรียบง่าย แต่สำหรับการออกแบบที่ซับซ้อนกว่านั้น จะช่วยประหยัดความพยายามได้อย่างมาก

2. การเข้ารหัส RTL

ขั้นต่อไป วิศวกรจะสร้างหรือปรับแต่งโค้ด นักออกแบบจะลงรายละเอียดเกี่ยวกับรีจิสเตอร์เฉพาะ การดำเนินการที่จำเป็น และการไหลของข้อมูล ส่วนสำคัญของขั้นตอนนี้คือการใช้โมดูลเพื่ออธิบายการดำเนินการทั่วไปและส่วนต่างๆ ของระบบ เมื่อสร้างโมดูลแล้ว สามารถนำโมดูลกลับมาใช้ซ้ำได้ตามต้องการ ซึ่งช่วยลดความซับซ้อนของการออกแบบโดยรวมได้อย่างมาก

3. การเพิ่มประสิทธิภาพการทำงาน กำลังไฟฟ้า และพื้นที่ (PPA)

เมื่อเขียนโค้ดเสร็จสิ้น การเพิ่มประสิทธิภาพก็จะเริ่มต้นขึ้น เป้าหมายของขั้นตอนนี้คือการปรับปรุงประสิทธิภาพ ลดการใช้พลังงาน และลดขนาดทางกายภาพของการออกแบบ

การจำลองเวลาและตรรกะ

เครื่องมือจำลองถูกนำมาใช้เพื่อวิเคราะห์เวลาและตรวจสอบค่ารีจิสเตอร์ทั่วทั้งระบบ การออกแบบจะถูกทดสอบที่ระดับการถ่ายโอนรีจิสเตอร์ เพื่อให้แน่ใจว่าไม่มีปัญหาเรื่องเวลาเกิดขึ้นทั่วทั้งวงจร และการทำงานให้ผลลัพธ์ตามที่คาดหวัง นี่คือจุดที่ทีมออกแบบจะลงมือแก้ไขปัญหาต่างๆ ในระบบ รวมถึงปัญหาด้านแหล่งจ่ายไฟโดยเร็วที่สุดในกระบวนการออกแบบ

ความจุโดยประมาณ

อุปกรณ์ทุกชิ้นในระบบใช้พลังงานในปริมาณหนึ่ง วิศวกรออกแบบจำเป็นต้องทราบปริมาณการใช้พลังงานและดำเนินการออกแบบซ้ำๆ เพื่อให้เข้าใจการกระจายพลังงานและลดการใช้พลังงาน ซอฟต์แวร์ Ansys PowerArtist™ ถูกใช้งานโดยบริษัทออกแบบเซมิคอนดักเตอร์ชั้นนำหลายแห่งเพื่อวิเคราะห์ จัดทำโปรไฟล์ และลดการใช้พลังงานในระดับการถ่ายโอนรีจิสเตอร์ ซอฟต์แวร์นี้มอบความเร็วในการประมวลผลที่รวดเร็ว ช่วยให้ทีมออกแบบสามารถวิเคราะห์และกระจายพลังงาน ระบุโค้ด RTL ที่ไม่มีประสิทธิภาพด้านพลังงาน และติดแท็กสวิตช์ที่สิ้นเปลืองในการออกแบบ

ลดพื้นที่ให้เหลือน้อยที่สุด

แต่ละส่วนประกอบในวงจรรวมใช้พื้นที่ทางกายภาพ เช่นเดียวกับการจัดเส้นทางระหว่างส่วนประกอบเหล่านั้น แม้ว่ากระบวนการออกแบบ RTL จะไม่ได้คำนึงถึงขนาดทางกายภาพของส่วนประกอบ แต่กระบวนการนี้จะบันทึกจำนวนส่วนประกอบและความซับซ้อนของการเชื่อมต่อระหว่างส่วนประกอบเหล่านั้น

4. การตรวจสอบ

เมื่อออกแบบแล้ว จำเป็นต้องตรวจสอบเพื่อให้แน่ใจว่าเป็นไปตามข้อกำหนดทั้งหมด ซึ่งถือเป็นส่วนสำคัญของกระบวนการออกแบบ และต้องตรวจสอบข้อกำหนดการออกแบบทั้งหมดก่อนจึงจะสามารถดำเนินการออกแบบได้ ซึ่งสามารถทำได้โดยใช้การจำลอง RTL หรือการตรวจสอบอย่างเป็นทางการ

การจำลอง RTL: มีการใช้เครื่องมือซอฟต์แวร์ต่างๆ เพื่อตรวจสอบการออกแบบแบบไดนามิก โดยนำเวกเตอร์อินพุตมาใช้และนำเวกเตอร์เอาต์พุตที่ได้ไปเปรียบเทียบกับผลลัพธ์ที่คาดหวัง อินพุตและเอาต์พุตมักจะแสดงเป็นรูปคลื่น เพื่อให้วิศวกรออกแบบสามารถตรวจสอบพฤติกรรมของระบบได้อย่างชัดเจน

การตรวจสอบอย่างเป็นทางการ: เป็นกระบวนการตรวจสอบแบบคงที่ที่ใช้ระบบอัตโนมัติเพื่อแปลงชุดความคาดหวังเชิงพฤติกรรมเป็นอัลกอริทึมทางคณิตศาสตร์ที่สำรวจพื้นที่ปฏิบัติการทั้งหมดของระบบ จากนั้นผลลัพธ์จะถูกประเมินทางคณิตศาสตร์เพื่อตรวจสอบความถูกต้อง

5. การสังเคราะห์ RTL

เมื่อการออกแบบระบบได้รับการตรวจสอบอย่างสมบูรณ์แล้ว การสังเคราะห์ RTL จะถูกใช้เพื่อแปลงการแสดงรหัส HDL ของการออกแบบ RTL ให้เป็นเน็ตลิสต์ระดับเกต นี่คืออินเทอร์เฟซสำหรับเครื่องมือที่แปลงแผนผังวงจรที่ได้เป็นโครงร่างทางกายภาพในเครื่องมือออกแบบอิเล็กทรอนิกส์อัตโนมัติ (EDA) บริษัทต่างๆ เช่น Synopsys ได้ผสานรวมเครื่องมือสังเคราะห์จำนวนมากเข้ากับแพลตฟอร์ม EDA ของตน

การใช้การออกแบบ RTL ในกระบวนการออกแบบ FPGA และ ASIC

วงจรรวมสามารถแบ่งได้เป็นสองประเภท วงจรรวมเฉพาะแอปพลิเคชัน (ASIC) ได้รับการออกแบบมาโดยเฉพาะสำหรับการใช้งานหรืองานเฉพาะ เมื่อผลิตแล้ว ตรรกะในชิปจะไม่สามารถเปลี่ยนแปลงได้ ตัวอย่างของชิป ASIC ได้แก่ โมดูลหน่วยความจำ เครื่องบันทึกดิจิทัล ตัวประมวลผลสัญญาณที่ปรับแต่งแล้ว ไมโครโปรเซสเซอร์ หน่วยประมวลผลกลาง (CPU) หรือแม้แต่ระบบที่ซับซ้อน เช่น ระบบบนชิปที่ประกอบด้วย I/O, CPU, หน่วยความจำ ฯลฯ

ชิป FPGA (Field-programmable Gate Array) คือชิปเซมิคอนดักเตอร์ที่สามารถตั้งโปรแกรมใหม่ได้หลังจากการผลิต แทนที่จะสร้างตรรกะไว้ในรูปทรงเรขาคณิตภายในของชิป FPGA จะมีอาร์เรย์ของบล็อกตรรกะที่เชื่อมต่อกันด้วยกริดเชื่อมต่อ ซึ่งสามารถตั้งโปรแกรมได้เช่นกัน

การออกแบบ RTL มีบทบาทคล้ายคลึงกันในระยะแรกของกระบวนการออกแบบทั้งสองแบบ เมื่อการสังเคราะห์ RTL เสร็จสมบูรณ์ กระบวนการออกแบบ ASIC จำเป็นต้องให้วิศวกรวางแผนและวางผังวงจรทางกายภาพ ซึ่งเป็นกระบวนการที่เรียกว่า Floor Planning ในการออกแบบ FPGA โค้ด RTL จะถูกแปลงเป็นเน็ตลิสต์โดยตรง ซึ่งจะระบุบล็อกตรรกะที่มีอยู่ และกำหนดค่าบล็อกเหล่านั้นในขั้นตอนการวางตำแหน่งและการกำหนดเส้นทาง

อนาคตของการออกแบบ RTL

การใช้ภาษาอธิบายฮาร์ดแวร์เพื่อแสดงพฤติกรรมที่ต้องการของระบบดิจิทัลเริ่มต้นขึ้นในช่วงทศวรรษ 1970 และ 1980 ภาษาเหล่านี้ได้รับความนิยมอย่างมากเมื่อเทคโนโลยี VLSI (Very Large Scale Integration) แพร่หลายมากขึ้น และก้าวทันการพัฒนาด้านการออกแบบวงจรรวม (IC) เมื่อขนาดของส่วนประกอบวงจรรวมลดลงอย่างต่อเนื่อง ความเร็วสัญญาณนาฬิกาเพิ่มขึ้นอย่างต่อเนื่อง และมีการผสานรวมฟังก์ชันต่างๆ ลงในชิปตัวเดียวมากขึ้น วิศวกรออกแบบจึงต้องเผชิญกับความท้าทายที่เพิ่มมากขึ้น

ความซับซ้อนในการออกแบบยังคงเพิ่มขึ้นอย่างต่อเนื่อง และเครื่องมือ RTL ยังคงพัฒนาอย่างต่อเนื่องเพื่อรับมือกับความท้าทายเหล่านี้ บริษัทต่างๆ ที่พัฒนาชุดเครื่องมือที่นักออกแบบจะนำมาใช้เพื่อพัฒนาวงจรรวมรุ่นต่อไป กำลังมุ่งเน้นไปที่หลายส่วนสำคัญเพื่อปรับปรุงความสะดวกในการใช้งาน ความสามารถ และฟังก์ชันการทำงานของกระบวนการออกแบบ RTL ประเด็นสำคัญที่มุ่งเน้น ได้แก่:

• ความจุลดลง

- การจัดการพลังงานยังคงเป็นหนึ่งในความท้าทายที่ใหญ่ที่สุดในกระบวนการออกแบบวงจรรวมทั้งหมด และการปรับประสิทธิภาพ RTL ยังคงเป็นโซลูชันหลักสำหรับการทำความเข้าใจและจัดการระดับการสูญเสียพลังงานในระบบ การปรับปรุงเครื่องมือต่างๆ เช่น ซอฟต์แวร์ PowerArtist ซึ่งมีตัวเลือกมากขึ้น การมองเห็นที่ดีขึ้น และความเร็วที่เร็วขึ้น จะช่วยให้ทีมงานสามารถรับมือกับความท้าทายนี้ได้

• การบูรณาการที่ราบรื่นระหว่าง เครื่องมือต่างๆ

- เมื่อจำนวนเครื่องมือออกแบบ จำลอง ตรวจสอบ และยืนยันความถูกต้องเพิ่มขึ้น ความสามารถของเครื่องมือที่มีอยู่ก็จะเพิ่มขึ้นตามไปด้วย บริษัทที่จัดหาเครื่องมือเหล่านี้และองค์กรในอุตสาหกรรมอย่าง IEEE จะต้องพัฒนาและปรับปรุงมาตรฐาน รวมถึงจัดหาเครื่องมือที่ทำให้การไหลของข้อมูลระหว่างแอปพลิเคชันเป็นไปอย่างราบรื่นที่สุด

• รวม AI ไว้ในกระบวนการออกแบบ

เครื่องมือหลายอย่างที่ใช้ในกระบวนการออกแบบวงจรรวมได้ใช้การเรียนรู้ของเครื่อง (ML) และระบบผู้เชี่ยวชาญเพื่อเร่งขั้นตอนกระบวนการ โดยเฉพาะอย่างยิ่งในการวางผังวงจรทางกายภาพ การพัฒนานี้จะยังคงดำเนินต่อไปด้วยอัลกอริทึม ML ที่ได้รับการปรับปรุงและการใช้เครื่องมือปัญญาประดิษฐ์ (AI) เพื่อแนะนำขั้นตอนต่อไปหรือแนวทางแก้ไขปัญหาที่เป็นไปได้มากที่สุด

• การปรับปรุงการสังเคราะห์ระดับสูง

ผู้จำหน่าย RTL กำลังทำงานเพื่อปรับปรุงความสามารถของวิศวกรในการแปลข้อมูลจำเพาะระบบระดับสูงเป็นภาษาฮาร์ดแวร์ระดับสูงด้วยความเร็วที่เร็วขึ้นและการออกแบบที่ใกล้เคียงกับการกำหนดค่าที่เหมาะสมที่สุด

• การสังเคราะห์ RTL ที่ชาญฉลาดยิ่งขึ้น

- จะมีศักยภาพในการเพิ่มผลผลิตและเพิ่มประสิทธิภาพอย่างมีนัยสำคัญเมื่อเกตในคำอธิบาย RTL ถูกแปลงเป็นทรานซิสเตอร์จริงในระหว่างขั้นตอนการสังเคราะห์ RTL เมื่อนำรูปทรงเรขาคณิตเชิงกายภาพมารวมไว้ในการออกแบบ จะมีโอกาสในการตัดสินใจอย่างชาญฉลาด ซึ่งจะช่วยลดความซับซ้อนของกระบวนการในการวางผังวงจรต่อไป

ผลิตภัณฑ์

December 20, 2025

การออกแบบระดับการถ่ายโอนทะเบียน (RTL) คืออะไร?

การออกแบบระดับการถ่ายโอนรีจิสเตอร์ (RTL) เป็นวิธีการอธิบายวิธีการเคลื่อนย้ายและประมวลผลข้อมูลระหว่างรีจิสเตอร์ในวงจรดิจิทัล

by

นักเขียนบทความ