ผลิตภัณฑ์

19

Jan

การแบ่งพาร์ติชัน SoC และการดำเนินการที่ประสบความสำเร็จ

คู่มือครอบคลุมเกี่ยวกับการแบ่งพาร์ติชัน SoC และการดำเนินการที่ประสบความสำเร็จ

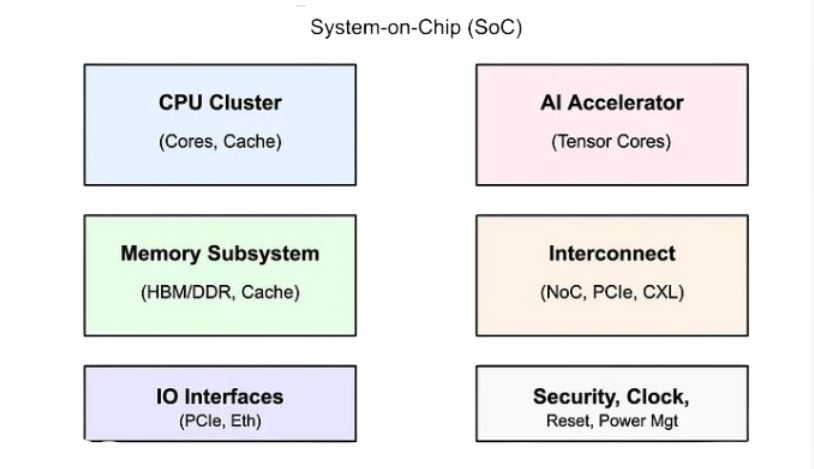

การออกแบบระบบบนชิป (System-on-Chip: SoC) เป็นกระบวนการที่ซับซ้อนซึ่งเกี่ยวข้องกับโมดูลฟังก์ชันจำนวนมาก ซึ่งแต่ละโมดูลมีข้อกำหนดเฉพาะของตนเอง การแบ่งพาร์ติชันเป็นวิธีการสำคัญที่ใช้จัดการความซับซ้อนโดยการแบ่ง SoC ออกเป็นบล็อกที่จัดการได้และเชื่อมโยงกัน กระบวนการนี้ส่งผลต่อประสิทธิภาพการออกแบบ ประสิทธิภาพการทำงาน และความสามารถในการผลิต

พาร์ติชันลอจิคัล

การแบ่งพาร์ติชันเชิงตรรกะคือการแบ่งส่วนการออกแบบ SoC ตามขอบเขตการทำงานและเชิงตรรกะ วิธีนี้ช่วยให้มั่นใจได้ว่าฟังก์ชันต่างๆ จะถูกรวมไว้ในโมดูลหรือระบบย่อยที่กำหนดไว้

แนวทางปฏิบัติที่ดีที่สุด

- การวิเคราะห์การทำงาน: ระบุฟังก์ชั่นหลักและจัดสรรให้กับพาร์ติชันที่เฉพาะเจาะจง

- คำจำกัดความอินเทอร์เฟซ: กำหนดโปรโตคอลการสื่อสารและกลไกการแลกเปลี่ยนข้อมูลระหว่างพาร์ติชันอย่างชัดเจน

- เพิ่มประสิทธิภาพลำดับชั้น: การตั้งค่าลำดับชั้นช่วยลดการพึ่งพากันและเพิ่มการทำงานแบบโมดูลาร์ให้สูงสุด

พาร์ติชันทางกายภาพ

การแบ่งโซนทางกายภาพเกี่ยวข้องกับการแบ่งเลย์เอาต์ SoC ออกเป็นพื้นที่ทางกายภาพหรือบล็อกบนชิป ขั้นตอนนี้มุ่งเน้นไปที่การจัดวาง การกำหนดเส้นทาง และการบรรลุเป้าหมายการออกแบบทางกายภาพ เช่น การปิดเวลาและประสิทธิภาพการใช้พลังงาน

แนวทางปฏิบัติที่ดีที่สุด

- การวางแผนไซต์: พัฒนาเค้าโครงที่เหมาะสมที่สุดเพื่อสร้างสมดุลระหว่างประสิทธิภาพ พลังงาน และพื้นที่ (PPA)

- ตำแหน่งคลัสเตอร์: การจัดกลุ่มคลัสเตอร์เชิงตรรกะที่เกี่ยวข้องทางกายภาพเพื่อประโยชน์ด้านเวลาและความจุ

- กลยุทธ์การจัดเส้นทาง: ลดความยาวของสายให้เหลือน้อยที่สุดและจัดการความแออัดได้อย่างมีประสิทธิภาพ

โมดูลที่ทำซ้ำได้: ระบุโมดูลตรรกะที่ทำซ้ำได้ หากโมดูลสามารถทำซ้ำได้ การแบ่งพาร์ติชันทางกายภาพจะมีข้อได้เปรียบที่สำคัญ เช่น การดำเนินการตามคำสั่งและเส้นทางเพียงครั้งเดียว และการประทับเวลา N ครั้ง วิธีนี้มีประโยชน์อย่างยิ่งในระหว่างการดีบักคำสั่งเปลี่ยนแปลงทางวิศวกรรมที่สำคัญ (ECOs) ในขั้นตอนสายพานลำเลียง

พิจารณาพื้นที่: ตรวจสอบให้แน่ใจว่าการแบ่งพาร์ติชันโมดูลจะไม่ทำให้เกิดค่าใช้จ่ายด้านพื้นที่จำนวนมาก หากการแบ่งพาร์ติชันทำให้เกิดปัญหาพื้นที่เพิ่มเติม แสดงว่าการแบ่งพาร์ติชันไม่เหมาะสม

พาร์ติชันลอจิคัลเทียบกับพาร์ติชันทางกายภาพ

การพึ่งพากันและการแลกเปลี่ยนผลประโยชน์

การแบ่งโซนเชิงตรรกะเป็นตัวกำหนดข้อจำกัดของรูปแบบทางกายภาพ ในขณะที่ความเป็นไปได้ทางกายภาพอาจต้องมีการปรับเปลี่ยนขอบเขตเชิงตรรกะ สิ่งสำคัญคือต้องพิจารณาปัจจัยทั้งสองนี้

ความสำคัญของการแบ่งพาร์ติชันในการออกแบบ SoC

ประโยชน์ของการแบ่งพาร์ติชั่นอย่างมีประสิทธิภาพ

- การจัดการการออกแบบที่ได้รับการปรับปรุง: ลดความซับซ้อนของการออกแบบ SoC ให้เป็นหน่วยที่เล็กลงและจัดการได้ง่ายขึ้น

- การพัฒนาแบบคู่ขนาน: ช่วยให้สามารถทำงานพร้อมกันระหว่างทีมได้

- การดีบักขั้นสูง: อำนวยความสะดวกในการดีบักและการตรวจสอบที่ตรงเป้าหมาย

- ออกแบบเพื่อการใช้ซ้ำ: ส่งเสริมการใช้ IP ซ้ำในทุกโครงการ

ความท้าทายของการแบ่งเขตที่ไม่ดี

- ความซับซ้อนที่เพิ่มขึ้น: การแบ่งพาร์ติชันที่ไม่ชัดเจนอาจนำไปสู่ความสัมพันธ์ที่พึ่งพากัน ตัวอย่างเช่น ผู้ออกแบบอาจเลือกที่จะเพิ่มรีจิสเตอร์ ซึ่งอาจส่งผลให้เกิดเกตใหม่ที่ขอบเขตของพาร์ติชัน ซึ่งจะส่งผลกระทบต่อการออกแบบทางกายภาพ

- ปัญหาคอขวดด้านเวลา: การแบ่งพาร์ติชั่นที่ไม่เหมาะสมอาจทำให้เกิดการละเมิดเวลา รันไทม์ยาวนาน และการตรวจสอบเวลาที่ไม่สำเร็จ

จุดเยือกแข็งของพาร์ติชั่น

เมื่อใดจึงควรแช่แข็งพาร์ติชัน

- การแบ่งพาร์ติชันเชิงตรรกะ: หยุดการทำงานหลังจากการตรวจสอบฟังก์ชันและการอนุมัติ RTL

- การแบ่งโซนทางกายภาพ: หยุดกระบวนการวางผังพื้นและเพิ่มประสิทธิภาพตำแหน่งเริ่มต้น

สิ่งที่ต้องแช่แข็งในพาร์ติชั่นลอจิคัลและฟิสิคัล

- การแบ่งพาร์ติชันเชิงตรรกะ: อินเทอร์เฟซ โปรโตคอลการสื่อสาร และขอบเขตการทำงาน

- การแบ่งเขตทางกายภาพ: แผนผังชั้น ตำแหน่งบล็อก และเส้นทางเดินรถหลัก

กรณีศึกษาและตัวอย่างจากโลกแห่งความเป็นจริง

สถานการณ์ความสำเร็จที่ 1: SoC มือถือ

ภูมิหลัง: SoC มือถือจะรวม CPU, GPU, โมเด็ม, DSP และระบบย่อย I/O เข้าในชิปตัวเดียว โดยมุ่งหวังให้สมาร์ทโฟนมีประสิทธิภาพสูงและใช้พลังงานต่ำ

กลยุทธ์การแบ่งเขตพื้นที่:

- ทีมออกแบบแบ่ง SoC ออกเป็นโดเมนพลังงาน (เช่น คอร์ CPU ในโดเมนหนึ่ง GPU ในอีกโดเมนหนึ่ง โมเด็มในโดเมนที่สาม) เพื่อให้สามารถจัดการพลังงานได้อย่างอิสระ

- อินเทอร์เฟซความเร็วสูง (เช่น PCIe, USB) จะถูกแยกทางกายภาพจากบล็อกการประมวลผลเพื่อลดสัญญาณรบกวนและปรับให้ความสมบูรณ์ของสัญญาณเหมาะสมที่สุด

ความสำเร็จ :

- ประสิทธิภาพการใช้พลังงาน: เทคโนโลยีการควบคุมแรงดันไฟฟ้าและความถี่แบบไดนามิก (DVFS) ทำงานได้อย่างราบรื่นในทุกพาร์ติชั่น ช่วยลดการใช้พลังงานลงได้ถึง 30% ภายใต้สภาวะการทำงานแบบไม่ได้ใช้งานหรือโหลดต่ำ

- การจัดการความร้อน: การแยกทางกายภาพของบล็อกสร้างความร้อน (CPU/GPU) ช่วยให้ระบายความร้อนได้ดีขึ้น หลีกเลี่ยงการลดประสิทธิภาพการระบายความร้อน

- เข้าสู่ตลาดได้เร็วขึ้น: ขอบเขตการแบ่งพาร์ติชันที่ชัดเจนช่วยให้ทีมต่างๆ สามารถพัฒนาไปพร้อมๆ กันได้ (เช่น ทีม CPU ทีม GPU)

บทเรียนที่ได้รับ:

- การระบุโดเมนพลังงานและโปรโตคอลอินเทอร์เฟซในระยะเริ่มต้นถือเป็นกุญแจสำคัญในการหลีกเลี่ยงปัญหาการรวมระบบ

- ควรหลีกเลี่ยงการแบ่งพาร์ติชันที่มากเกินไป เนื่องจากบล็อกเล็กมากเกินไปอาจเพิ่มความซับซ้อนในการกำหนดเส้นทางและพื้นที่ได

สถานการณ์อันตราย 1: การแบ่งพาร์ติชันมากเกินไปใน SoC ของยานยนต์

ภูมิหลัง: SoC ของยานยนต์ที่ออกแบบมาสำหรับระบบช่วยเหลือผู้ขับขี่ขั้นสูง (ADAS) ต้องมีการประมวลผลแบบเรียลไทม์ ความซ้ำซ้อนที่สำคัญต่อความปลอดภัย และความหน่วงต่ำ

กลยุทธ์การแบ่งเขตพื้นที่:

- ทีมงานได้แบ่งการออกแบบออกเป็นบล็อกเล็กๆ หลายบล็อกอย่างจริงจัง (เช่น พาร์ติชันแยกสำหรับอินเทอร์เฟซเซ็นเซอร์ โปรเซสเซอร์ และตัวควบคุมหน่วยความจำแต่ละตัว) เพื่อเพิ่มความสามารถในการสร้างโมดูลและการนำกลับมาใช้ใหม่ให้สูงสุด

ข้อผิดพลาด:

- ค่าใช้จ่ายในการเชื่อมต่อ: พาร์ติชันมากเกินไปทำให้การเชื่อมต่อบนชิป (NoC) มีขนาดใหญ่ขึ้น ส่งผลให้เวลาแฝงเพิ่มขึ้น 15% และใช้พื้นที่ไดมากกว่าที่วางแผนไว้ 20%

- ปัญหาการปิดเวลา: การกำหนดเส้นทางสัญญาณระหว่างพาร์ติชั่นกลายเป็นคอขวด ทำให้เกิดความล่าช้าในการตอบสนองข้อกำหนดเวลา

- ความท้าทายในการตรวจสอบ: ความซับซ้อนในการรวมพาร์ติชันต่างๆ มากมายทำให้ทีมงานตรวจสอบรับภาระไม่ไหว ส่งผลให้การเผยแพร่เทปล่าช้าไปสามเดือน

บทเรียนที่ได้รับ:

- ความสมดุลระหว่างการทำงานแบบโมดูลาร์และการใช้งานจริง — พาร์ติชันที่ใหญ่และน้อยลงสามารถทำให้การกำหนดเส้นทางและการตรวจสอบง่ายขึ้น

- จำลองประสิทธิภาพการเชื่อมต่อในช่วงเริ่มต้นของขั้นตอนการออกแบบเพื่อตรวจจับปัญหาความล่าช้าและพื้นที่

- การแบ่งโซนเกินเพื่อนำมาใช้ใหม่ในอนาคตอาจมีความเสี่ยงหากระยะเวลาโครงการและเป้าหมาย PPA ในปัจจุบันได้รับผลกระทบ

สถานการณ์ความสำเร็จที่ 2: ตัวเร่งความเร็ว AI

บริบท: AI SoC ที่ออกแบบมาสำหรับเวิร์กโหลดการเรียนรู้ของเครื่องนั้นต้องใช้หน่วยประมวลผลแบบขนานขนาดใหญ่ หน่วยความจำแบนด์วิดท์สูง (HBM) และการเชื่อมต่อที่รวดเร็ว

กลยุทธ์การแบ่งเขตพื้นที่:

- การออกแบบแบ่งออกเป็นคลัสเตอร์การประมวลผล (เช่น คอร์โปรเซสเซอร์) ตัวควบคุมหน่วยความจำ และบล็อก I/O

- คลัสเตอร์การคำนวณจะถูกจำลองแบบสมมาตรทั่วทั้งได ในขณะที่อินเทอร์เฟซ HBM จะถูกวางไว้ใกล้ขอบเพื่อให้แน่ใจว่ามีความสมบูรณ์ของสัญญาณที่เหมาะสมที่สุด

ความสำเร็จ :

- ความสามารถในการปรับขนาด: พาร์ติชันการคำนวณแบบโมดูลาร์ช่วยให้ขยายได้ง่าย (เช่น เพิ่มจำนวนคอร์เป็นสองเท่าในรุ่นถัดไป) โดยไม่ต้องออกแบบชิปใหม่ทั้งหมด

- การเพิ่มประสิทธิภาพแบนด์วิดท์: การวางตัวควบคุมหน่วยความจำไว้ใกล้กับ HBM จะช่วยลดเวลาแฝงและเพิ่มปริมาณงานได้ 40% เมื่อเปรียบเทียบกับการออกแบบหน่วยความจำแบบรวมศูนย์

- เพิ่มประสิทธิภาพการผลิต: การแบ่งพาร์ติชันช่วยให้สามารถแยกข้อผิดพลาดได้ โดยสามารถปิดการใช้งานคลัสเตอร์การคำนวณที่ผิดพลาดได้ ช่วยให้ไดที่ทำงานบางส่วนยังปลอดภัย

บทเรียนที่ได้รับ:

- ความสมมาตรในการแบ่งพาร์ติชันสามารถทำให้เค้าโครงเรียบง่ายขึ้นและปรับปรุงการผลิตได้

- ความใกล้ชิดของอินเทอร์เฟซความเร็วสูงกับการเชื่อมต่อภายนอกเป็นสิ่งสำคัญต่อประสิทธิภาพการทำงาน

- การออกแบบเพื่อการทดสอบ (DFT) และความซ้ำซ้อนควรจะรวมเข้าไว้ในพาร์ติชันเพื่อเพิ่มประสิทธิภาพการผลิตให้สูงสุด

สถานการณ์อันตรายที่ 2: SoC สัญญาณผสม (เช่น อุปกรณ์ IoT)

บริบท: IoT SoC ผสมผสานลอจิกดิจิทัล (ไมโครคอนโทรลเลอร์, สแต็กไร้สาย) กับส่วนประกอบอนาล็อก (ตัวรับส่งสัญญาณ RF, ADC) บนชิปตัวเดียว

กลยุทธ์การแบ่งเขตพื้นที่:

- ในตอนแรก ทีมงานได้วางบล็อกดิจิทัลและแอนะล็อกไว้ใกล้กันเพื่อลดพื้นที่ได โดยคิดว่าวงแหวนการ์ดและการป้องกันจะช่วยลดสัญญาณรบกวนได้

ข้อผิดพลาด:

- การเชื่อมต่อสัญญาณรบกวน: สัญญาณรบกวนจากการสลับแบบดิจิทัลรั่วไหลเข้าไปในบล็อก RF อะนาล็อก ทำให้อัตราส่วนสัญญาณต่อสัญญาณรบกวน (SNR) ลดลง 10 dB และทำให้ระยะสัญญาณไร้สายลดลง 25%

- ต้นทุนการทำงานซ้ำ: การออกแบบใหม่ในระยะหลังเพื่อแยกพาร์ติชันอะนาล็อกและดิจิทัลออกจากกันทำให้ระยะเวลาในกำหนดการเพิ่มขึ้น 6 เดือนและเพิ่มต้นทุนขึ้น 15%

- ปัญหาการจ่ายพลังงาน: การวางแผนแยกกริดที่ไม่เพียงพอส่งผลให้แรงดันไฟฟ้าตกในส่วนอะนาล็อกระหว่างกิจกรรมดิจิทัลสูงสุด

บทเรียนที่ได้รับ:

- การแยกทางกายภาพระหว่างโดเมนอะนาล็อกและดิจิทัลนั้นไม่สามารถต่อรองได้ จึงควรเลือกการแยกตัวมากกว่าการประหยัดพื้นที่

- จำลองสัญญาณรบกวนและการกระจายพลังงานระหว่างพาร์ติชั่นช่วงต้นโดยใช้เครื่องมือจำลองสัญญาณผสม

- จัดสรรโซนบัฟเฟอร์หรือพื้นที่ว่างระหว่างบล็อกที่มีความละเอียดอ่อนเพื่อให้แน่ใจว่าสามารถใช้การออกแบบได้ในอนาคต

แนวโน้มการแบ่งพาร์ติชัน SoC

การแบ่งพาร์ติชันการออกแบบทางกายภาพในการพัฒนาระบบบนชิป (SoC) เกี่ยวข้องกับการแบ่งเค้าโครงชิปออกเป็นพื้นที่ทางกายภาพที่แตกต่างกันเพื่อปรับตำแหน่ง การจัดวาง การกระจายพลังงาน และผลผลิตให้เหมาะสมที่สุด วิธีการใหม่ๆ เช่น การแบ่งพาร์ติชันด้วย AI การออกแบบวงจรรวม 3 มิติขั้นสูง และการเชื่อมต่อแบบไฮบริด กำลังเปลี่ยนแปลงกระบวนการนี้ ต่อไปนี้ ผมจะศึกษาว่าแต่ละวิธีส่งผลต่อการตัดสินใจแบ่งพาร์ติชันทางกายภาพในขั้นตอนการออกแบบแบ็กเอนด์อย่างไร

การแบ่งพาร์ติชันทางกายภาพที่ขับเคลื่อนด้วย AI

AI กำลังถูกผสานเข้าในเครื่องมือออกแบบทางกายภาพเพื่อทำให้การแบ่งเค้าโครงชิปเป็นบล็อกทางกายภาพเป็นอัตโนมัติและเหมาะสมที่สุด ซึ่งจะช่วยปรับปรุงประสิทธิภาพของเค้าโครงและการวางแผนไซต์

วิธีการทำงาน:

- อินพุต: โมเดล AI ใช้เน็ตลิสต์ ข้อจำกัดด้านเวลา งบประมาณพลังงาน และข้อมูลโหนดกระบวนการ (เช่น กฎการออกแบบ 5 นาโนเมตร) เพื่อแนะนำขอบเขตบล็อกทางกายภาพ

- การวิเคราะห์: อัลกอริทึมจะทำนายความแออัด ความยาวของสายไฟ และความต้องการของกริด แนะนำการแบ่งพาร์ติชันเพื่อลดความซับซ้อนของการกำหนดเส้นทางหรือการสูญเสีย IR

- การใช้งาน: AI ทำการวนซ้ำผังพื้นโดยปรับเปลี่ยนรูปร่างบล็อกและตำแหน่งพิน เช่น การจัดกลุ่มลอจิกความเร็วสูงใกล้กับแป้นพิมพ์ I/O เพื่อลดความหน่วงของสัญญาณ

เอื้ออำนวย :

- การลดความแออัด: ใน SoC ที่ซับซ้อน AI สามารถแบ่งบล็อกลอจิกหนาแน่นออกเป็นสองภูมิภาคที่เล็กกว่า ซึ่งจะช่วยลดความแออัดของการกำหนดเส้นทางลง 15% และลดเวลาในการปิดลง

- การเพิ่มประสิทธิภาพการใช้พลังงาน: AI สามารถจัดกลุ่มโมดูลพลังงานต่ำเป็นพาร์ติชั่นเดียว ทำให้ลดพื้นที่โครงข่ายไฟฟ้าลง 10%

- ระบบอัตโนมัติ: เวลาในการวางแผนพื้นที่ลดลงจากหลายสัปดาห์เหลือเพียงไม่กี่วัน เนื่องจาก AI ประเมินเค้าโครงหลายพันแบบเทียบกับเป้าหมาย PPA (ความจุ ประสิทธิภาพ พื้นที่)

ท้าทาย :

- ความแม่นยำ: AI อาศัยข้อมูลการฝึกอบรม หากไม่มีเค้าโครงล่วงหน้าสำหรับโหนดกระบวนการใหม่ การคาดการณ์อาจพลาดผลทางกายภาพที่ละเอียดอ่อน เช่น จุดร้อนของการพิมพ์หินด้วยแสง

- การรวมระบบ: เครื่องมือ EDA ที่มีอยู่ (เช่น การวางและการกำหนดเส้นทางการไหล) อาจไม่รองรับพาร์ติชันที่ขับเคลื่อนด้วย AI อย่างสมบูรณ์ ซึ่งต้องมีการปรับแต่งด้วยตนเอง

- ค่าใช้จ่ายเพิ่มเติม: การปรับแต่งคำแนะนำ AI อย่างละเอียดสามารถเพิ่มความซับซ้อนได้ หากการแบ่งพาร์ติชั่นเบื้องต้นไม่ตรงกับขั้นตอนถัดไป เช่น การสังเคราะห์ต้นไม้สัญญาณนาฬิกา

ผลกระทบต่อพาร์ติชันทางกายภาพ:

- AI เปลี่ยนการแบ่งพาร์ติชันทางกายภาพจากการลองผิดลองถูกด้วยตนเองไปสู่การเพิ่มประสิทธิภาพเชิงคาดการณ์ ยกตัวอย่างเช่น ใน SoC บนมือถือ AI สามารถสร้างพาร์ติชันสี่เหลี่ยมผืนผ้าสำหรับ GPU ใกล้กับขอบชิป ซึ่งช่วยให้มั่นใจได้ว่าเส้นทางไปยังพินหน่วยความจำภายนอกจะสั้นลง ซึ่งเป็นการตัดสินใจที่ผ่านการตรวจสอบด้วยเมตริกความยาวสายที่ลดลง

การออกแบบ IC 3D ขั้นสูงในการแบ่งพาร์ติชันทางกายภาพ

ภาพรวม: ไอซี 3 มิติจะวางซ้อนไดหลายตัวในแนวตั้งโดยใช้เวสิเคิลซิลิคอนทะลุ (TSV) เพื่อเชื่อมต่อพาร์ติชั่นทางกายภาพข้ามหลายชั้น โดยขยายพาร์ติชั่นไปยังแกน z ในระหว่างการออกแบบทางกายภาพ

วิธีการทำงาน:

- กลยุทธ์การแบ่งพาร์ติชัน: บล็อกทางกายภาพได้รับการกำหนดให้กับไดแยกกัน เช่น ลอจิกการคำนวณบนเลเยอร์หนึ่ง SRAM บนอีกเลเยอร์หนึ่ง โดยขึ้นอยู่กับความต้องการความใกล้ชิดและการเชื่อมต่อ

- การพิจารณาเค้าโครง: TSV จะถูกวางอย่างมีกลยุทธ์ในพาร์ติชันเพื่อเชื่อมต่อชั้นต่างๆ เข้าด้วยกัน ซึ่งต้องมีการจัดตำแหน่งอย่างระมัดระวังในระหว่างการออกแบบเค้าโครง

- ตัวอย่างเช่น ใน SoC ประสิทธิภาพสูง การออกแบบทางกายภาพอาจแบ่งบล็อกแคชขนาดใหญ่ลงในไดด้านบน ซึ่งอยู่เหนือหน่วยประมวลผล โดยที่ TSV จัดการการถ่ายโอนข้อมูลแนวตั้ง

เอื้ออำนวย :

- ความยาวสายลดลง: การซ้อนช่วยลดการเดินสายแนวนอนได้มากถึง 50% เนื่องจากสัญญาณแพร่กระจายในแนวตั้งผ่าน TSV แทนที่จะแพร่กระจายไปทั่วระนาบ 2 มิติ

- ความหนาแน่น: SoC สัญญาณผสมสามารถแยกบล็อกแอนะล็อกออกเป็นบล็อกหนึ่งที่ด้านล่างและลอจิกดิจิทัลที่ด้านบน ทำให้ขนาดพื้นที่ 2 มิติเล็กลงในขณะที่แยกภูมิภาคที่ไวต่อสัญญาณรบกวนออกไป

- ผลผลิต: การแบ่งบล็อกที่มีข้อบกพร่องออกเป็นหลายชั้นทำให้สามารถใช้แม่พิมพ์ได้บางส่วน ทำให้การผลิตโดยรวมดีขึ้น

ท้าทาย :

- ผลกระทบจากความร้อน: พาร์ติชั่นที่สร้างความร้อน (เช่น คอร์ CPU) บนชั้นบนสุดสามารถทำให้ไดด้านล่างร้อนเกินไป ส่งผลให้การจัดวางทางกายภาพมีความซับซ้อน

- ต้นทุน TSV: TSV แต่ละตัวจะใช้พื้นที่เค้าโครง (เช่น ระยะห่าง 5–10µm) ทำให้ต้องมีพาร์ติชันที่ใหญ่กว่าหรือการออกแบบที่เบาบางกว่าเพื่อรองรับ TSV แต่ละตัว

- การจัดตำแหน่ง: TSV ที่ไม่ได้จัดตำแหน่งในระหว่างการซ้อนจะรบกวนกระบวนการกำหนดเส้นทาง ซึ่งต้องใช้การวางแผนพื้นที่แม่นยำบนแม่พิมพ์ต่างๆ

ผลกระทบต่อพาร์ติชันทางกายภาพ:

- ไอซี 3 มิติต้องการกลยุทธ์การแบ่งโซนแนวตั้ง นักออกแบบสามารถแยกตัวควบคุมหน่วยความจำออกจากบล็อกลอจิกบนไดย์สองอัน โดยวางอาร์เรย์ TSV ไว้ที่ขอบของการแบ่งโซนเพื่อปรับเส้นทางสัญญาณให้เหมาะสมที่สุด ซึ่งตัวเลือกนี้ขับเคลื่อนโดยความหนาแน่นของเลย์เอาต์และการทำแผนที่ความร้อน

บทบาทของลิงก์ไฮบริดในการแบ่งพาร์ติชันทางกายภาพ

ภาพรวม: การเชื่อมต่อแบบไฮบริดจะเชื่อมต่อแผ่นทองแดงระหว่างไดที่วางซ้อนกันโดยตรงโดยไม่มี TSV ทำให้สามารถเชื่อมต่อด้วยระยะห่างที่เล็กมาก (เช่น 1µm) และกำหนดความละเอียดของพาร์ติชันทางกายภาพใหม่ในระบบไดหลายตัว

วิธีการทำงาน:

- กระบวนการ: แม่พิมพ์จะเชื่อมต่อกันด้วยการเชื่อมต่อทองแดงกับทองแดง ทำให้แผ่นกั้นสามารถขยายขอบเขตของแม่พิมพ์ได้โดยมีระยะห่างน้อยที่สุด

- แอปพลิเคชันการแบ่งพาร์ติชัน: บล็อกทางกายภาพสามารถแบ่งได้ในระดับที่ละเอียดมากขึ้น เช่น พาร์ติชันเดียว เช่น DSP สามารถครอบคลุมไดสองได โดยมีแผ่นรองเชื่อมต่อมาแทนที่รูทะลุแบบดั้งเดิม

- ตัวอย่างเช่น ใน IoT SoC โครงร่างทางกายภาพของตัวรับส่งสัญญาณ RF สามารถอยู่บนไดหนึ่ง โดยเชื่อมติดกับพาร์ติชั่นดิจิทัลบนไดอีกอันโดยตรง หลีกเลี่ยงภูมิภาคที่ห้ามใช้ TSV

เอื้ออำนวย :

- ความหนาแน่นของอินเตอร์คอนเนคต์: ด้วยระยะห่างที่ต่ำถึง 1µm อินเตอร์คอนเนคต์แบบไฮบริดจึงรองรับการเชื่อมต่อได้มากกว่า TSV ถึง 10 เท่าต่อขอบพาร์ติชั่น ช่วยให้จัดวางได้แน่นหนายิ่งขึ้น

- ความสมบูรณ์ของสัญญาณ: ปรสิตที่ลดลงจะปรับปรุงการจับเวลา ช่วยให้สามารถวางพาร์ติชันให้ใกล้กับ I/O ที่สำคัญได้โดยไม่เสื่อมสภาพ

- การประหยัดพื้นที่: การกำจัด TSV จะช่วยเพิ่มพื้นที่เค้าโครง ช่วยให้นักออกแบบสามารถลดขนาดพาร์ติชันหรือรวมฟังก์ชันการทำงานเพิ่มเติมลงในแต่ละไดได้

ท้าทาย :

- ความแม่นยำในการจัดวาง: การยึดติดต้องมีความแม่นยำในระดับต่ำกว่าไมครอน ดังนั้นขอบเขตของพาร์ติชันจะต้องจัดวางให้ตรงกันอย่างสมบูรณ์แบบในระหว่างการออกแบบแผนผัง ซึ่งจะเพิ่มความพยายามในการออกแบบ

- การยึดติดด้วยความร้อน: การยึดติดโดยตรงจะถ่ายเทความร้อนระหว่างพาร์ติชั่นได้อย่างมีประสิทธิภาพมากขึ้น จึงจำเป็นต้องวางจุดร้อนอย่างระมัดระวัง

- ต้นทุน: ความแม่นยำในการผลิตที่สูงจำกัดการยึดติดแบบไฮบริดไว้เฉพาะกับการออกแบบระดับไฮเอนด์เท่านั้น ซึ่งส่งผลต่อการแบ่งต้นทุนและผลประโยชน์

ผลกระทบต่อพาร์ติชันทางกายภาพ:

- การเชื่อมต่อแบบไฮบริดช่วยให้สามารถแบ่งพาร์ติชันแบบหลายไดได้อย่างราบรื่น สำหรับ SoC ที่ใช้การประมวลผลสูง บล็อกตรรกะขนาดใหญ่สามารถแบ่งออกเป็นไดที่เชื่อมต่อกันสองได โดยมีแผ่นเชื่อมต่อวางอยู่ตามขอบทางกายภาพของพาร์ติชันเพื่อรักษาความต่อเนื่อง ลดความจำเป็นในการใช้ช่องสัญญาณการจัดเส้นทางที่กว้าง

ข้อควรพิจารณาในการออกแบบทางกายภาพโดยเฉพาะ

- ผลกระทบจากการทำงานร่วมกันในการวางผังพื้น: AI สามารถเพิ่มประสิทธิภาพเค้าโครง 3 มิติและการเชื่อมต่อแบบไฮบริดได้ด้วยการทำนาย TSV หรือตำแหน่งแผ่นเชื่อมต่อ เพื่อให้แน่ใจว่าพาร์ติชั่นจะสอดคล้องกับโครงข่ายไฟฟ้าและแผนผังนาฬิกา

- ผลกระทบต่อการกำหนดเส้นทาง: IC 3 มิติช่วยลดความแออัดของการกำหนดเส้นทาง 2 มิติ แต่ก่อให้เกิดความท้าทายในการเชื่อมต่อแนวตั้ง ในขณะที่อินเตอร์คอนเนกต์แบบไฮบริดจะบรรเทาทั้งสองอย่าง ช่วยให้มีอินเทอร์เฟซที่แบ่งพาร์ติชันหนาแน่นมากขึ้น

- ความสามารถในการผลิต: การแบ่งเขตจะต้องคำนึงถึงกฎเกณฑ์เฉพาะกระบวนการ เช่น แบนด์แก๊ป TSV ในไอซี 3 มิติหรือแพดเชื่อมต่อในแบบไฮบริด ซึ่งควบคุมขนาดและรูปร่างของบล็อกทางกายภาพ

ตัวอย่างในบริบทฟิสิกส์:

- ขับเคลื่อนโดย AI: ใน SoC ของเซิร์ฟเวอร์ AI สามารถแบ่งบล็อกที่เชื่อมต่อกันอย่างหนาแน่นออกเป็นสองภูมิภาคสี่เหลี่ยมผืนผ้า โดยวางไว้ใกล้ขอบตรงข้ามเพื่อสร้างสมดุลให้กับเลเยอร์การกำหนดเส้นทาง

- 3D IC: การออกแบบทางกายภาพของ SoC มือถืออาจวางพาร์ติชั่น GPU ไว้ด้านบนของพาร์ติชั่น CPU โดยมี TSV รวมกันอยู่ที่ขอบด้านล่างของ GPU เพื่อจ่ายพลังงาน

- การเชื่อมต่อแบบไฮบริด: ตัวเร่งความเร็ว AI สามารถแบ่งพาร์ติชันหน่วยความจำออกเป็นสองไดโดยใช้การเชื่อมต่อแบบไฮบริดเพื่อจัดเรียงสายแคชโดยตรงข้ามหน่วยประมวลผล ช่วยลดเวลาแฝงในการเข้าถึง

สรุป

การแบ่งพาร์ติชัน SoC ที่มีประสิทธิภาพเป็นรากฐานสำคัญของผลลัพธ์การออกแบบที่ประสบความสำเร็จ ด้วยการทำความเข้าใจความแตกต่างของการแบ่งพาร์ติชันเชิงตรรกะและเชิงกายภาพ ความแตกต่าง และความสำคัญของการตัดสินใจแบบ Freeze วิศวกรจึงสามารถรับมือกับความซับซ้อนของการพัฒนา SoC สมัยใหม่ได้อย่างมั่นใจ

ผลิตภัณฑ์

December 20, 2025

การแบ่งพาร์ติชัน SoC และการดำเนินการที่ประสบความสำเร็จ

คู่มือครอบคลุมเกี่ยวกับการแบ่งพาร์ติชัน SoC และการดำเนินการที่ประสบความสำเร็จ

by

นักเขียนบทความ