ผลิตภัณฑ์

19

Jan

การเชื่อมต่อสัญญาณรบกวนของสารตั้งต้นในวงจรรวม

บทความนี้จะตรวจสอบกลไกและเทคนิคการบรรเทาผลกระทบสำหรับการจับคู่สัญญาณรบกวนพื้นผิว ซึ่งเป็นปัญหาสำคัญที่ส่งผลต่อความสมบูรณ์ของสัญญาณในวงจรรวม

วงจรรวมซิลิคอนใช้การแยกรูปแบบต่างๆ เพื่อแยกอุปกรณ์ทางไฟฟ้า เช่น รอยต่อ PN แบบไบอัสย้อนกลับ หรือการแยกร่อง ยกเว้นวัสดุพิเศษ เช่น ซิลิคอนบนแซฟไฟร์ วงจรทั้งหมดใช้ซับสเตรตซิลิคอน ซึ่งเป็นเส้นทางที่อาจเกิดการต่อสัญญาณรบกวน การต่อสัญญาณรบกวนนี้อาจลดประสิทธิภาพการทำงานหรืออาจถึงขั้นทำให้การทำงานล้มเหลวได้ ดังนั้น นักออกแบบจึงจำเป็นต้องใช้เทคนิคต่างๆ เพื่อลดการเกิดการต่อสัญญาณรบกวนให้น้อยที่สุด

โดยทั่วไปมีสารตั้งต้นหลายประเภทที่แตกต่างกัน:

- ความต้านทานสูง ใช้สำหรับ RF ที่ต้องการการสูญเสียต่ำสำหรับอุปกรณ์ เช่น ตัวเหนี่ยวนำและตัวเก็บประจุบนชิป

- epi ชนิด P ที่พัฒนาบนซับสเตรต P+ มักถูกใช้สำหรับลอจิกดิจิทัล การผสมผสานระหว่างซับสเตรตที่มีความต้านทานต่ำซึ่งช่วยป้องกันแลตช์ และ epi ที่มีความต้านทานสูงเพื่อประสิทธิภาพของอุปกรณ์นั้นเป็นไปได้อย่างสมบูรณ์แบบ

- ชั้นฝังที่มีความต้านทานต่ำและชั้นฝังที่มีความต้านทานสูงสำหรับกระบวนการสองขั้ว

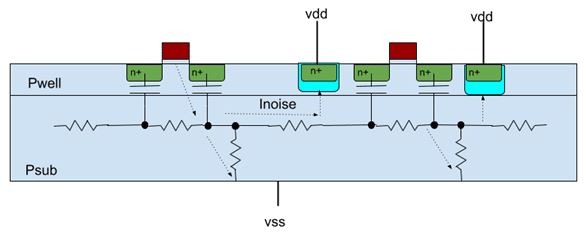

ในรูปที่ 1 เราแสดงกรณีทั่วไปที่มีอุปกรณ์ NMOS 2 ตัวใน P-die ทั่วไป ที่ความถี่ต่ำพอ (< 10 GHz) ไดจะถือว่าเป็นตัวต้านทานล้วนๆ ดังนั้นการเชื่อมต่อสัญญาณรบกวนจึงเกิดขึ้นผ่านรอยต่อ PN และตัวไดเป็นหลัก

ในตัวอย่างข้างต้น สัญญาณรบกวนอาจถูกนำเข้าสู่พื้นผิวจากหลายแหล่ง:

- การแตกตัวของไอออนที่กระทำในช่องของอุปกรณ์ MOS

- การเชื่อมต่อแบบคาปาซิทีฟจากสัญญาณรบกวนระหว่างจุดเชื่อมต่อ PN

- แพ็กเกจ RLC ทำให้เกิดไฟกระชากเนื่องจากการเปลี่ยนแปลงพลังงานอย่างกะทันหันและเอฟเฟกต์ Ldi/dt

สัญญาณรบกวนสามารถแพร่กระจายผ่านไดไปยังบริเวณที่ละเอียดอ่อนของวงจรได้ โดยทั่วไป สัญญาณรบกวนสามารถเกิดจากบล็อกดิจิทัลที่สลับเร็วซึ่งเชื่อมต่อกับบล็อกอะนาล็อก ซึ่งความผันผวนของแรงดันไฟฟ้าของไดอาจทำให้ค่า Vt ของอุปกรณ์เปลี่ยนแปลง ทำให้เกิดความแปรผันของอัตราขยาย เครื่องมือเชิงพาณิชย์สามารถวิเคราะห์การต่อเชื่อมสัญญาณรบกวนของได โดยทั่วไปโดยการสร้างตาข่าย RC ของได เมื่อพิจารณาจากโปรไฟล์การเจือปนของจุดเชื่อมต่อและหลุมต่างๆ สภาพต้านทานของไดสามารถถูกแบ่งย่อยเพื่อสร้างตาข่าย RC ซึ่งสามารถแก้ปัญหาได้โดยใช้วิธีการไฟไนต์เอลิเมนต์หรือองค์ประกอบขอบเขตเพื่อคำนวณแรงดันไฟฟ้าและกระแสไฟฟ้าตามเวลาและ/หรือความถี่ อย่างไรก็ตาม การวิเคราะห์แบบเต็มรูปแบบมีความซับซ้อนและใช้เวลานาน ดังนั้นนักออกแบบหลายคนจึงใช้เทคนิคที่ผ่านการพิสูจน์แล้วเพื่อลดปัญหาสัญญาณรบกวนจากได

ในกรณีที่ง่ายที่สุดสำหรับอุปกรณ์ใน P-substrate (รูปที่ 2) วงแหวนป้องกัน P+ รอบๆ อุปกรณ์ที่มีความละเอียดอ่อนและ/หรือรอบๆ เครื่องส่งสัญญาณเสียงรบกวนสามารถลดการจับคู่สัญญาณรบกวนของพื้นผิวลงเหลือ 30dB ได้ [1]

อีกวิธีหนึ่งคือการใช้วงแหวนป้องกันทิศตะวันตกเฉียงเหนือ (NW) เชื่อมต่อกับ VDD เพื่อสร้างรอยต่อ PN แบบไบอัสย้อนกลับ (รูปที่ 3) วิธีนี้ช่วยลดสัญญาณรบกวนได้ดีขึ้น โดยเฉพาะที่ความถี่ต่ำ ซึ่งอิมพีแดนซ์ของตัวเก็บประจุที่รอยต่อมีค่ามากกว่าค่าความต้านทานฐาน แต่กินพื้นที่มากกว่า

แนวทางที่สามใช้ NW ลึกเพื่อแยกอุปกรณ์ใน P-well ของตัวเอง ซึ่งให้การแยกที่ดียิ่งขึ้น (รูปที่ 4) ต้องใช้ความระมัดระวังกับเน็ตเวิร์กที่เชื่อมต่อ DNW อยู่ ในตอนแรก การเชื่อมต่อกับ VDD อาจดูเหมือนถูกต้องเพื่อกลับขั้วของรอยต่อ PN อย่างไรก็ตาม หากเชื่อมต่อกับ VDD ทั่วไป ซึ่งกำลังไฟฟ้าพุ่งสูงขึ้นเนื่องจากความเหนี่ยวนำของสายบรรจุภัณฑ์หรือสายเชื่อมต่อ มันจะทำหน้าที่เป็นตัวส่งสัญญาณรบกวนที่รุนแรงไปยัง P-well ที่แยกจากกันเนื่องจากความจุของรอยต่อพื้นที่ขนาดใหญ่ การเชื่อมต่อ DNW เข้ากับ VSS โดยเฉพาะอย่างยิ่งควรแยกออกจาก VSS ส่วนที่เหลือบนชิป สามารถป้องกันปัญหานี้ได้

โดยสรุป สัญญาณรบกวนพื้นหลังเป็นปัญหาสำคัญสำหรับวงจรดิจิทัลความเร็วสูงที่ตั้งอยู่บนซับสเตรตเดียวกันกับวงจรอนาล็อกหรือ RF ที่มีความไวสูง สัญญาณรบกวนพื้นหลังอาจลดประสิทธิภาพการทำงานหรืออาจถึงขั้นทำให้ทำงานผิดปกติได้ การใช้วงแหวนป้องกันอย่างระมัดระวังสามารถช่วยลดสัญญาณรบกวนพื้นหลังได้โดยการเพิ่มพื้นที่ใช้งานเล็กน้อย

ผลิตภัณฑ์

December 20, 2025

การเชื่อมต่อสัญญาณรบกวนของสารตั้งต้นในวงจรรวม

บทความนี้จะตรวจสอบกลไกและเทคนิคการบรรเทาผลกระทบสำหรับการจับคู่สัญญาณรบกวนพื้นผิว ซึ่งเป็นปัญหาสำคัญที่ส่งผลต่อความสมบูรณ์ของสัญญาณในวงจรรวม

by

นักเขียนบทความ