ผลิตภัณฑ์

19

Jan

การตัดแต่งเชิงเส้น

เรียนรู้วิธีการตัดแต่งความเป็นเส้นตรง (Linearity Trimming) เพื่อลดความผิดเพี้ยนให้เหลือน้อยที่สุด เพื่อการประมวลผลสัญญาณที่ไร้ที่ติ

บทนำเกี่ยวกับการตัดแต่งเชิงเส้น

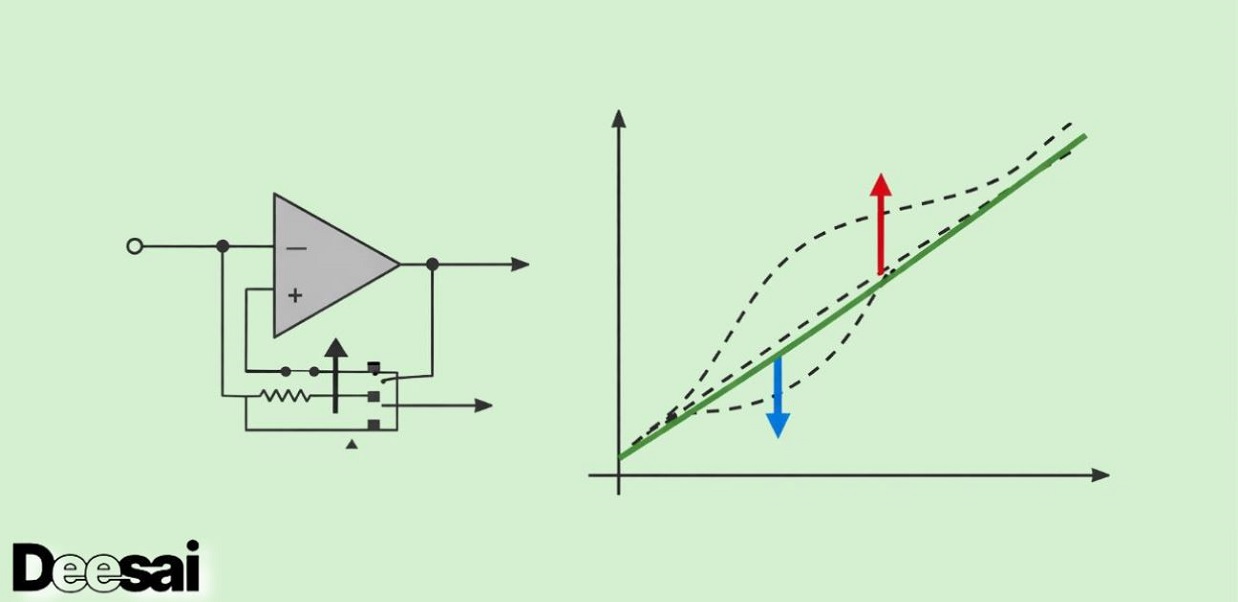

การปรับแต่งความเป็นเชิงเส้น (Linearity trimming) เป็นกระบวนการที่สำคัญอย่างยิ่งในตัวแปลงสัญญาณอนาล็อกเป็นดิจิทัล (ADC) โดยมีเป้าหมายเพื่อรับประกันความเป็นเชิงเส้นของฟังก์ชันการถ่ายโอน (transfer function) ซึ่งทำหน้าที่แปลงสัญญาณอนาล็อกขาเข้าเป็นสัญญาณดิจิทัลขาออก ความแม่นยำนี้มีความสำคัญอย่างยิ่งต่อการสร้างสัญญาณอนาล็อกขึ้นมาใหม่ในรูปแบบดิจิทัลได้อย่างถูกต้องแม่นยำ

วัตถุประสงค์และความจำเป็น

วัตถุประสงค์: วัตถุประสงค์หลักของการปรับแต่งความเป็นเชิงเส้นคือการปรับเทียบและแก้ไขความไม่เป็นเชิงเส้นใดๆ ที่มีอยู่ในฟังก์ชันการถ่ายโอนของ ADC ในสถานการณ์ที่เหมาะสม ADC จะสร้างเอาต์พุตที่แปรผันตรงกับอินพุต อย่างไรก็ตาม ADC ในทางปฏิบัติอาจแสดงความเบี่ยงเบนจากความเป็นเชิงเส้นในอุดมคตินี้เนื่องจากปัจจัยต่างๆ เช่น ความคลาดเคลื่อนของส่วนประกอบ ความผันผวนของอุณหภูมิ และความคลาดเคลื่อนในการผลิต การปรับแต่งความเป็นเชิงเส้นจึงทำหน้าที่ปรับแต่งคุณลักษณะของ ADC ให้ใกล้เคียงกับผลตอบสนองเชิงเส้นในอุดมคติมากขึ้น

ความจำเป็น: ในการใช้งานที่ต้องการความแม่นยำสูง เช่น ในเครื่องมือวัด อุปกรณ์ทางการแพทย์ และระบบเสียงคุณภาพสูง ความไม่เป็นเชิงเส้นภายใน ADC อาจนำไปสู่ข้อผิดพลาดและการบิดเบือนอย่างมากในการแสดงผลสัญญาณอนาล็อกในรูปแบบดิจิทัล เพื่อให้แน่ใจว่าเอาต์พุตดิจิทัลสะท้อนอินพุตอนาล็อกได้อย่างถูกต้องตลอดช่วงการทำงานทั้งหมด การปรับแต่งความเป็นเชิงเส้นจึงกลายเป็นสิ่งจำเป็นอย่างยิ่ง

แนวคิดของ DNL และ INL

ความไม่เป็นเชิงเส้นเชิงอนุพันธ์ (Differential Non-Linearity: DNL): DNL ทำหน้าที่เป็นตัววัดปริมาณความคลาดเคลื่อนที่เกิดขึ้นระหว่างความกว้างจริงของแต่ละขั้นรหัสกับความกว้างของขั้นรหัสที่คาดการณ์ไว้ ซึ่งโดยทั่วไปกำหนดไว้ที่ 1 บิตที่มีนัยสำคัญน้อยที่สุด (Least Significant Bit: LSB) ในโลกของตัวแปลงสัญญาณอนาล็อกเป็นดิจิทัล (Analog-to-Digital Converter: ADC) ในอุดมคติ เราคาดหวังว่าความกว้างของแต่ละรหัสจะตรงกับ 1 LSB อย่างแม่นยำ อย่างไรก็ตาม ในความเป็นจริงของ ADC ที่ใช้งานได้จริง ความสอดคล้องที่สมบูรณ์แบบนี้มักจะหาได้ยาก ดังนั้น DNL จึงเข้ามามีบทบาทในการกำหนดลักษณะความแปรผันระหว่างความกว้างของขั้นรหัสจริงกับ 1 LSB ที่คาดการณ์ไว้ เมื่อ DNL อยู่ในช่วง -1 ถึง +1 LSB แสดงว่าไม่มีรหัสใดถูกละเว้นหรือหายไปในฟังก์ชันการถ่ายโอนของ ADC

ค่าความไม่เป็นเชิงเส้นแบบอินทิกรัล (INL): INL เป็นค่าที่วัดปริมาณความเบี่ยงเบนของฟังก์ชันถ่ายโอนของ ADC จากเส้นตรงในอุดมคติ เส้นตรงนี้อาจเป็นเส้นตรงที่เหมาะสมที่สุดหรือเส้นที่เชื่อมต่อจุดปลายของฟังก์ชันถ่ายโอนก็ได้ INL วัดค่าความแตกต่าง ซึ่งแสดงในหน่วย LSB ระหว่างตำแหน่งจริงของแต่ละรหัสกับเส้นตรงที่กำหนดไว้ ค่า INL ที่ต่ำกว่าแสดงถึง ADC ที่เป็นเชิงเส้นมากขึ้น ซึ่งบ่งชี้ถึงการจัดเรียงที่ดีกว่ากับผลตอบสนองเชิงเส้นในอุดมคติ

ทั้ง DNL และ INL ถือเป็นพารามิเตอร์สำคัญในการประเมินความเป็นเชิงเส้นของ ADC เทคนิคที่ใช้ในการปรับแต่งความเป็นเชิงเส้นนั้นมุ่งเน้นไปที่การลดความคลาดเคลื่อนเหล่านี้เป็นหลัก ซึ่งจะช่วยเพิ่มประสิทธิภาพของ ADC โดยเฉพาะอย่างยิ่งในแอปพลิเคชันที่ต้องการความถูกต้องและเที่ยงตรงสูง

ในส่วนถัดไปจะเจาะลึกถึงกลยุทธ์แบบอนาล็อกและดิจิทัลที่หลากหลายสำหรับการปรับแต่งความเป็นเชิงเส้น โดยจะอธิบายถึงบทบาทและความสำคัญของกลยุทธ์เหล่านั้นในการเพิ่มประสิทธิภาพของ ADC

เทคนิคอนาล็อกสำหรับการปรับแต่งความเป็นเชิงเส้น

การประยุกต์ใช้เทคนิคอนาล็อกสำหรับการปรับแต่งความเป็นเชิงเส้นเกี่ยวข้องกับการปรับแต่งทางกายภาพของส่วนประกอบอนาล็อกภายในตัวแปลงอนาล็อกเป็นดิจิทัล (ADC) เพื่อเพิ่มความเป็นเชิงเส้นของฟังก์ชันการถ่ายโอน ในส่วนนี้จะเจาะลึกถึงสองเทคนิคอนาล็อกที่ใช้กันอย่างแพร่หลาย ได้แก่ การดัดแปลงวงจรตัวต้านทานแบบขั้นบันได และการปรับแหล่งจ่ายกระแส

การปรับบันไดตัวต้านทาน

ภายใน ADC นั้น วงจรตัวต้านทานแบบขั้นบันได เช่น วงจร R-2R มักถูกนำมาใช้เป็นส่วนประกอบสำคัญของตัวแปลงสัญญาณดิจิทัลเป็นอนาล็อก (DAC) ที่ฝังอยู่ภายใน ADC ความแม่นยำและความเป็นเชิงเส้นของวงจรตัวต้านทานแบบขั้นบันไดเหล่านี้มีบทบาทสำคัญในการกำหนดประสิทธิภาพของ ADC

เทคนิคการปรับค่า: การทำให้ค่าความต้านทานภายในวงจรแลดเดอร์มีความใกล้เคียงกันอย่างมากเป็นสิ่งสำคัญอย่างยิ่งต่อประสิทธิภาพที่แม่นยำ สามารถดำเนินการปรับแต่งได้ในระหว่างกระบวนการผลิต โดยใช้เทคนิคการตัดแต่งด้วยเลเซอร์อย่างพิถีพิถันเพื่อให้ได้ค่าความต้านทานที่ต้องการ หรืออีกทางเลือกหนึ่งคือ การใช้โพเทนชิโอมิเตอร์แบบดิจิทัล ซึ่งสามารถปรับค่าได้ผ่านรีจิสเตอร์ควบคุม ทำให้สามารถทำการสอบเทียบได้ในระหว่างการทำงานตามปกติ

ผลกระทบต่อความเป็นเชิงเส้น: การปรับปรุงการจับคู่ตัวต้านทานภายในโครงสร้างแบบขั้นบันไดส่งผลให้ลดข้อผิดพลาดจากความไม่เป็นเชิงเส้นแบบดิฟเฟอเรนเชียล (DNL) และความไม่เป็นเชิงเส้นแบบอินทิกรัล (INL) ดังนั้น การปรับปรุงนี้จึงช่วยเพิ่มความเป็นเชิงเส้นโดยรวมของ ADC ทำให้ได้ประสิทธิภาพที่แม่นยำและเที่ยงตรงยิ่งขึ้นในฟังก์ชันการแปลงสัญญาณดิจิทัลเป็นอนาล็อก

การปรับแหล่งกำเนิดกระแสไฟฟ้า

ในสถาปัตยกรรม ADC บางประเภท เช่น ADC แบบ successive approximation การสร้างแรงดันอ้างอิงจะใช้แหล่งจ่ายกระแสไฟฟ้า ความแม่นยำของแหล่งจ่ายกระแสไฟฟ้าเหล่านี้มีผลต่อระดับความเป็นเชิงเส้นของ ADC เป็นอย่างมาก

เทคนิคการปรับแต่ง: ขั้นตอนการปรับแต่งที่เกี่ยวข้องกับแหล่งจ่ายกระแสโดยทั่วไปนั้นเกี่ยวข้องกับการใช้ตัวสะท้อนกระแสแบบปรับได้ ซึ่งเกี่ยวข้องกับการปรับแรงดันเกตของทรานซิสเตอร์แบบ MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) ในตัวสะท้อนกระแส หรือการใช้แหล่งจ่ายกระแสแบบไบนารีที่มีการถ่วงน้ำหนักเพื่อกำหนดระดับกระแสที่ต้องการได้อย่างแม่นยำ นอกจากนี้ อีกทางเลือกหนึ่งคือการสอบเทียบภายนอกที่อำนวยความสะดวกผ่านอินเทอร์เฟซดิจิทัล วิธีการสอบเทียบนี้ช่วยให้สามารถจัดเก็บปัจจัยการแก้ไข ซึ่งสามารถนำไปใช้กับแหล่งจ่ายกระแสในระหว่างขั้นตอนการทำงานของ ADC ได้

ผลกระทบต่อความเป็นเชิงเส้น: การสอบเทียบและการปรับแหล่งกำเนิดกระแสอย่างพิถีพิถันมีความสำคัญอย่างยิ่งในการรักษาฟังก์ชันการถ่ายโอนเชิงเส้นของ ADC ความไม่แม่นยำหรือข้อผิดพลาดใดๆ ภายในแหล่งกำเนิดกระแสอาจทำให้เกิดลักษณะที่ไม่เป็นเชิงเส้นในแรงดันอ้างอิง ซึ่งส่งผลเสียต่อความเป็นเชิงเส้นโดยรวมของ ADC

เทคนิคดิจิทัลสำหรับการตัดแต่งเชิงเส้น

ในขณะที่เทคนิคแบบอนาล็อกสำหรับการปรับแต่งความเป็นเชิงเส้นนั้นเกี่ยวข้องกับการปรับแต่งส่วนประกอบทางกายภาพ เทคนิคแบบดิจิทัลจะอาศัยอัลกอริธึมและการประมวลผลข้อมูลเพื่อแก้ไขปัญหาความไม่เป็นเชิงเส้นภายใน ADC ในส่วนนี้ เราจะสำรวจเทคนิคดิจิทัลที่สำคัญสองเทคนิคที่ใช้สำหรับการปรับแต่งความเป็นเชิงเส้น ได้แก่ การวิเคราะห์ความหนาแน่นของรหัสและการแก้ไขข้อผิดพลาดแบบดิจิทัล

การวิเคราะห์ความหนาแน่นของรหัส

การวิเคราะห์ความหนาแน่นของรหัสเป็นวิธีการที่ใช้ในการตรวจสอบและแก้ไขข้อผิดพลาดของความไม่เป็นเชิงเส้นเชิงอนุพันธ์ (Differential Non-Linearity: DNL) ภายใน ADC หลักการพื้นฐานของเทคนิคนี้ขึ้นอยู่กับหลักการที่ว่า เมื่อได้รับสัญญาณอินพุตที่มีการกระจายอย่างสม่ำเสมอ ฮิสโตแกรมรหัสเอาต์พุตของ ADC ควรแสดงความสม่ำเสมอเช่นกัน

เทคนิค: เทคนิคนี้เริ่มต้นด้วยการป้อนสัญญาณอินพุตที่ทราบค่าและมีการกระจายแบบสม่ำเสมอเข้าไปใน ADC จากนั้นจึงตรวจสอบฮิสโตแกรมของรหัสเอาต์พุต การตรวจสอบนี้มีจุดประสงค์เพื่อระบุบริเวณภายใน ADC ที่เกิดข้อผิดพลาดความไม่เป็นเชิงเส้นแบบดิฟเฟอเรนเชียล (Differential Non-Linearity: DNL) การมีอยู่ของข้อผิดพลาด DNL จะปรากฏชัดเมื่อมีการเบี่ยงเบนจากการกระจายแบบสม่ำเสมอที่คาดไว้ในฮิสโตแกรมของรหัสเอาต์พุต

การแก้ไข: จากข้อมูลเชิงลึกที่ได้จากการวิเคราะห์ความหนาแน่นของรหัส สามารถสร้างปัจจัยการแก้ไขได้ ปัจจัยการแก้ไขเหล่านี้ถูกนำไปใช้ในการปรับรหัสเอาต์พุต โดยมีเป้าหมายเพื่อลดและบรรเทาผลกระทบของข้อผิดพลาด DNL กระบวนการแก้ไขนี้เกิดขึ้นในโดเมนดิจิทัล โดยทั่วไปจะดำเนินการภายในตัวประมวลผลสัญญาณดิจิทัล (DSP) หรือไมโครคอนโทรลเลอร์ ที่น่าทึ่งคือ กระบวนการนี้ดำเนินการโดยไม่ต้องแก้ไขส่วนประกอบอนาล็อกใดๆ ที่ประกอบเป็น ADC ซึ่งเน้นย้ำถึงลักษณะดิจิทัลของมัน

การแก้ไขข้อผิดพลาดดิจิทัล

เทคนิคการแก้ไขข้อผิดพลาดแบบดิจิทัลเป็นกลุ่มของวิธีการที่ใช้ในการแก้ไขข้อผิดพลาดทั้งแบบความไม่เป็นเชิงเส้นเชิงปริพันธ์ (Integral Non-Linearity: INL) และความไม่เป็นเชิงเส้นเชิงอนุพันธ์ (Differential Non-Linearity: DNL) ในตัวแปลงสัญญาณอนาล็อกเป็นดิจิทัล (Analog-to-Digital Converter: ADC) เทคนิคเหล่านี้มุ่งเน้นไปที่การปรับค่าทางคณิตศาสตร์กับเอาต์พุตดิจิทัลของ ADC เพื่อชดเชยอิทธิพลของความไม่เป็นเชิงเส้น

เทคนิค: วิธีการที่ใช้กันทั่วไปวิธีหนึ่งคือการใช้ตารางค้นหา (LUT) ที่เก็บค่าแก้ไขที่สอดคล้องกับรหัสเอาต์พุต ADC ที่แตกต่างกัน ค่าเอาต์พุตดิบจาก ADC จะทำหน้าที่เป็นดัชนีภายในตารางนี้ ทำให้สามารถดึงค่าที่แก้ไขแล้วที่สอดคล้องกับรหัสเอาต์พุตจาก LUT ได้

การสอบเทียบ: การพัฒนาตารางค้นหา (LUT) โดยทั่วไปจำเป็นต้องมีขั้นตอนการสอบเทียบ ในระหว่างการสอบเทียบ สัญญาณอินพุตที่ทราบค่าจะถูกป้อนเข้าสู่ ADC และรหัสเอาต์พุตที่ได้จะถูกเปรียบเทียบกับค่าที่คาดการณ์ไว้ ความคลาดเคลื่อนที่ระบุได้ในกระบวนการนี้จะถูกนำมาใช้เพื่อเติมค่าแก้ไขที่จำเป็นลงใน LUT

ข้อควรพิจารณาในการนำไปใช้งาน: สิ่งสำคัญที่ควรทราบคือ การประยุกต์ใช้เทคนิคการแก้ไขข้อผิดพลาดแบบดิจิทัลโดยทั่วไปแล้วจำเป็นต้องมีการจัดสรรทรัพยากรการประมวลผลและหน่วยความจำเพิ่มเติมสำหรับการจัดเก็บตารางค้นหา (LUT) หรืออัลกอริธึมการแก้ไข นอกจากนี้ สิ่งสำคัญคือต้องตระหนักว่าเทคนิคเหล่านี้อาจทำให้เกิดความหน่วงแฝงเพิ่มเติมในเอาต์พุตของ ADC ซึ่งเป็นปัจจัยที่อาจเป็นข้อกังวลในแอปพลิเคชันที่ความแม่นยำของเวลาเป็นสิ่งสำคัญยิ่ง

ผลิตภัณฑ์

January 19, 2026

การตัดแต่งเชิงเส้น

เรียนรู้วิธีการตัดแต่งความเป็นเส้นตรง (Linearity Trimming) เพื่อลดความผิดเพี้ยนให้เหลือน้อยที่สุด เพื่อการประมวลผลสัญญาณที่ไร้ที่ติ

by

นักเขียนบทความ