ผลิตภัณฑ์

19

Jan

ออกแบบอินเทอร์เฟซดิจิทัลที่เชื่อถือได้สำหรับ ADC แบบประมาณค่าต่อเนื่อง

บทความนี้ควรช่วยให้นักออกแบบตรวจสอบสาเหตุหลักและเสนอวิธีแก้ไข

การแนะนำ

ตัวแปลงอนาล็อกเป็นดิจิทัลแบบประมาณค่าต่อเนื่อง หรือที่รู้จักกันในชื่อ SAR ADC เนื่องจากมีรีจิสเตอร์ประมาณค่าแบบต่อเนื่อง เป็นที่นิยมสำหรับการใช้งานที่ต้องการความละเอียดสูงสุด 18 บิต ที่ความเร็วสูงสุด 5 MSPS ข้อดีของตัวแปลงสัญญาณเหล่านี้ ได้แก่ ขนาดเล็ก กินไฟต่ำ ไม่มีความล่าช้าของไพพ์ไลน์ และใช้งานง่าย

โปรเซสเซอร์โฮสต์สามารถเข้าถึงหรือควบคุม ADC ผ่านอินเทอร์เฟซแบบอนุกรมและแบบขนานที่หลากหลาย เช่น SPI, I2C และ LVDS บทความนี้จะกล่าวถึงเทคนิคการออกแบบสำหรับอินเทอร์เฟซดิจิทัลแบบบูรณาการที่เชื่อถือได้ ซึ่งรวมถึงระดับพลังงานดิจิทัลและลำดับ สถานะเปิด-ปิด I/O เวลาของอินเทอร์เฟซ คุณภาพสัญญาณ และข้อผิดพลาดที่เกิดจากการทำงานแบบดิจิทัล

ระดับพลังงาน I/O ดิจิทัลและการเรียงลำดับ

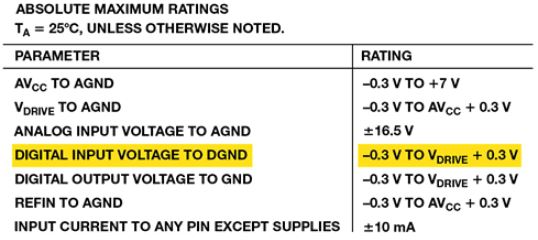

ADC SAR ส่วนใหญ่มีอินพุตพลังงาน I/O ดิจิทัลแยกต่างหาก คือ VIO หรือ VDRIVE ซึ่งกำหนดแรงดันไฟฟ้าในการทำงานและความเข้ากันได้ของลอจิกของอินเทอร์เฟซ พินนี้ต้องมีแรงดันไฟฟ้าเท่ากับแรงดันไฟฟ้าที่จ่ายให้กับอินเทอร์เฟซโฮสต์ (MCU, DSP หรือ FPGA) โดยทั่วไปอินพุตดิจิทัลจะอยู่ระหว่าง DGND -0.3 V และ VIO +0.3 V เพื่อหลีกเลี่ยงการเกินค่าสูงสุดสัมบูรณ์ ควรเชื่อมต่อตัวเก็บประจุแบบแยกส่วนที่มีไฟฟ้าลัดวงจรระหว่างพิน VIO และ DGND

ADC ที่ทำงานกับแหล่งจ่ายไฟหลายตัวสามารถมีลำดับแหล่งจ่ายไฟที่กำหนดไว้อย่างชัดเจน หมายเหตุการใช้งาน AN-932, ลำดับแหล่งจ่ายไฟ ให้ข้อมูลอ้างอิงที่เป็นประโยชน์สำหรับการออกแบบแหล่งจ่ายไฟสำหรับ ADC เหล่านี้ เพื่อหลีกเลี่ยงการเกิดไบอัสไปข้างหน้าของไดโอด ESD และการจ่ายไฟให้กับแกนดิจิทัลในสถานะที่ไม่ถูกกำหนด ให้จ่ายไฟให้กับวงจร I/O ก่อนวงจรอินเทอร์เฟซ โดยทั่วไปแหล่งจ่ายไฟแบบอนาล็อกจะจ่ายไฟก่อนแหล่งจ่ายไฟ I/O แต่ ADC ไม่ได้จ่ายไฟให้ทั้งหมด โปรดอ่านและปฏิบัติตามเอกสารข้อมูลเพื่อให้แน่ใจว่าการเรียงลำดับถูกต้อง

สถานะ I/O ดิจิทัลเมื่อเปิดใช้งาน

เพื่อการเริ่มต้นระบบอย่างถูกต้อง ADC แบบ SAR บางตัวจำเป็นต้องมีสถานะหรือลำดับตรรกะบางอย่างสำหรับฟังก์ชันดิจิทัล เช่น การรีเซ็ต การสแตนด์บาย หรือการปิดเครื่อง หลังจากแหล่งจ่ายไฟทั้งหมดมีเสถียรภาพแล้ว จะมีการใช้พัลส์ที่กำหนดหรือชุดพัลส์หลายชุดเพื่อให้แน่ใจว่า ADC จะเริ่มทำงานตามสถานะที่ต้องการ ตัวอย่างเช่น จำเป็นต้องใช้พัลส์รีเซ็ตความถี่สูงที่มีระยะเวลาอย่างน้อย 50 นาโนวินาที เพื่อกำหนดค่า AD7606 ให้ทำงานได้ตามปกติหลังจากเปิดเครื่อง

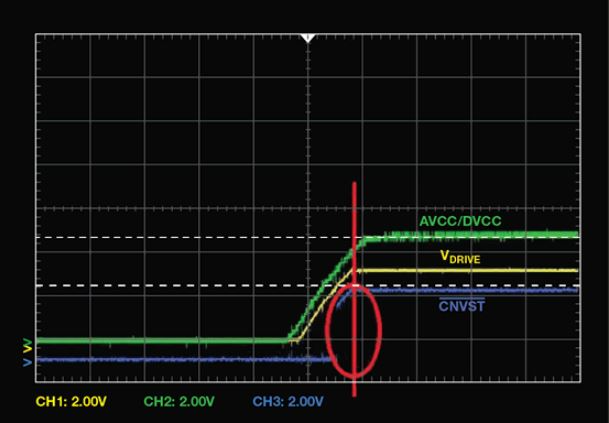

ไม่ควรเปิด/ปิดพินดิจิทัลจนกว่าแหล่งจ่ายไฟฟ้าทั้งหมดจะจ่ายไฟเต็ม สำหรับ SAR ADC พินเริ่มต้นการแปลง CNVST อาจไวต่อสัญญาณรบกวน รูปที่ 1 แสดงตัวอย่างที่โฮสต์ cPLD ขับเคลื่อน CNVST สูงในขณะที่ AVCC, DVCC และ VDRIVE ยังคงเร่งความเร็วอยู่ ซึ่งอาจทำให้ AD7367 เข้าสู่สถานะที่ไม่รู้จัก ดังนั้นโฮสต์ควรรักษา CNVST ให้อยู่ในระดับต่ำจนกว่าแหล่งจ่ายไฟฟ้าทั้งหมดจะจ่ายไฟเต็ม

เวลาอินเทอร์เฟซดิจิทัล

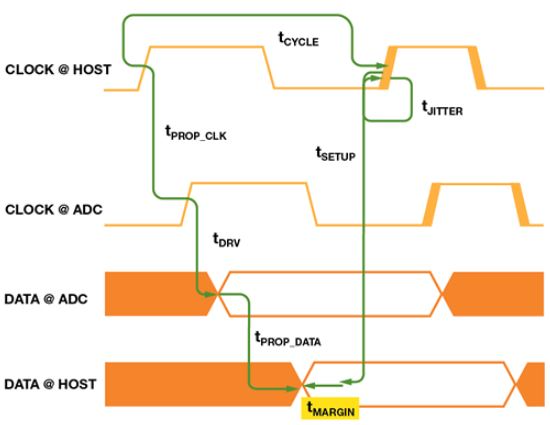

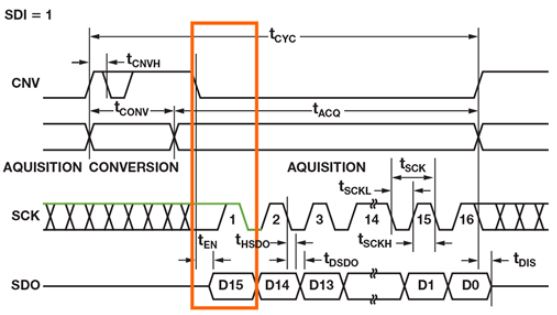

หลังจากการแปลงเสร็จสมบูรณ์ โฮสต์สามารถอ่านข้อมูลผ่านอินเทอร์เฟซแบบอนุกรมหรือแบบขนานได้ หากต้องการอ่านข้อมูลอย่างแม่นยำ ให้ปฏิบัติตามกลยุทธ์การกำหนดเวลาเฉพาะ เช่น โหมดที่ใช้สำหรับบัส SPI อย่าละเมิดข้อกำหนดการกำหนดเวลาอินเทอร์เฟซดิจิทัล โดยเฉพาะอย่างยิ่งเวลาการตั้งค่าและเวลาค้างของ ADC และโฮสต์ อัตราบิตสูงสุดถูกกำหนดโดยรอบการทำงานทั้งหมด ไม่ใช่แค่รอบสัญญาณนาฬิกาขั้นต่ำที่ระบุ รูปที่ 2 และสมการต่อไปนี้แสดงตัวอย่างวิธีการคำนวณแอมพลิจูดของการตั้งค่าและเวลาค้าง โฮสต์จะส่งสัญญาณนาฬิกาไปยัง ADC และอ่านข้อมูลเอาต์พุตจาก ADC

t CYCLE = t JITTER + t SETUP + t PROP_DATA + t PROP_CLK + t DRV + t MARGIN

tCYCLE : ช่วงเวลาของนาฬิกา = 1/ f CLOCK

tJITTER : ความสั่นไหวของนาฬิกา

tSETUP : เวลาการตั้งค่าเซิร์ฟเวอร์

tHOLD : เวลาการยึดของเซิร์ฟเวอร์

tPROP_DATA: ความล่าช้าในการส่งข้อมูลตามสายจาก ADC ไปยังโฮสต์

tPROP_CLK: ความล่าช้าในการแพร่กระจายสัญญาณนาฬิกาตามสายจากโฮสต์ไปยัง ADC

tDRV: เวลาที่ถูกต้องของเอาต์พุตข้อมูลหลังจากนาฬิกาขึ้น/ลง

t MARGIN: เวลาระยะขอบ ≥ 0 หมายถึง เวลาในการตั้งค่าหรือเวลาในการรอ < 0 หมายถึง ยังไม่ถึงเวลาตั้งค่าหรือเวลาในการรอ

ช่วงการตั้งค่าสำหรับเซิร์ฟเวอร์คือ

t MARGIN_SETUP = t CYCLE , minutes – t JITTER – t SETUP – t PROP_DATA – t PROP_CLK – t DRV, MAX

สมการกำหนดเวลาการตั้งค่าจะกำหนดเวลารอบสัญญาณนาฬิกาขั้นต่ำหรือความถี่สูงสุดโดยอิงจากค่าความหน่วงของระบบสูงสุด ค่านี้ต้อง ≥ 0 เพื่อให้เป็นไปตามข้อกำหนดเวลา เพิ่มช่วงเวลา (ลดความถี่สัญญาณนาฬิกา) เพื่อจัดการกับค่าความหน่วงของระบบที่มากเกินไป สำหรับบัฟเฟอร์ ตัวเลื่อนระดับ ตัวแยกสัญญาณ หรือส่วนประกอบเพิ่มเติมอื่นๆ บนบัส ให้เพิ่มค่าความหน่วงเพิ่มเติมให้กับ tPROP_CLK และ tPROP_DATA

ในทำนองเดียวกัน ระยะขอบที่เก็บไว้สำหรับเซิร์ฟเวอร์คือ

t MARGIN_HOLD = t PROP_DATA + t PROP_CLK + t DRV – t JITTER – t HOLD

สมการเวลาหน่วง (hold-up time) เป็นตัวกำหนดระยะเวลาหน่วงของระบบขั้นต่ำที่จำเป็นเพื่อหลีกเลี่ยงข้อผิดพลาดเชิงตรรกะอันเนื่องมาจากการละเมิดการหน่วง ความล่าช้านี้ต้องมีค่า ≥ 0 เพื่อให้เป็นไปตามข้อกำหนดเวลา

ADC SAR ADI ของอินเทอร์เฟซ SPI จำนวนมากจะติดตาม MSB จากขอบตกของ CS หรือ CNV ในขณะที่บิตข้อมูลที่เหลือจะติดตามขอบตกของ SCLK ดังที่แสดงในรูปที่ 3 เมื่ออ่านข้อมูล MSB ให้ใช้สิบในสมการแทน tDRV

ดังนั้น นอกเหนือจากอัตราสัญญาณนาฬิกาสูงสุดแล้ว ความเร็วการทำงานสูงสุดของอินเทอร์เฟซดิจิทัลยังขึ้นอยู่กับเวลาในการตั้งค่า เวลาในการยึด เวลาที่ถูกต้องของเอาต์พุตข้อมูล ความล่าช้าในการแพร่กระจาย และความสั่นไหวของสัญญาณนาฬิกาอีกด้วย

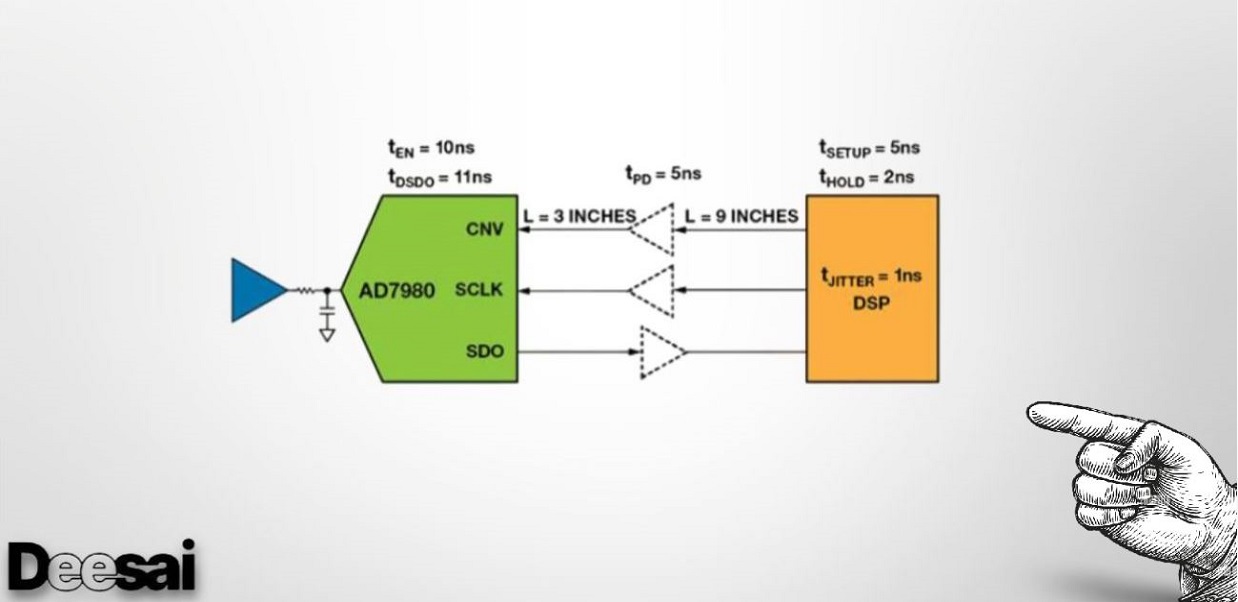

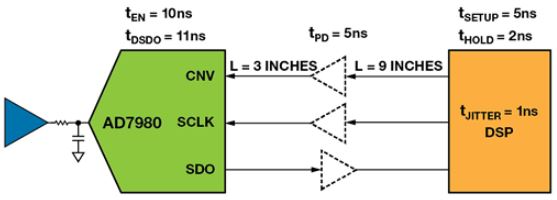

รูปที่ 4 แสดงโฮสต์ DSP ที่เข้าถึง AD7980 ในโหมด CS แบบ 3 สาย โดยมี VIO = 3.3 V DSP จะยึดสัญญาณ SDO ที่ขอบตกของ SCLK DSP กำหนดเวลาตั้งค่าขั้นต่ำที่ 5 นาโนวินาที และเวลาพักสัญญาณขั้นต่ำที่ 2 นาโนวินาที สำหรับบอร์ดพีซี FR-4 ทั่วไป ความล่าช้าในการแพร่กระจายอยู่ที่ประมาณ 180 ps/นิ้ว ความล่าช้าในการแพร่กระจายบัฟเฟอร์คือ 5 นาโนวินาที ความล่าช้าในการแพร่กระจายทั้งหมดสำหรับ CNV, SCLK และ SDO คือ

tprop = 180 ps/in × (9 in + 3 in) + 5 ns = 7 ns

tJITTER = 1 ns เซิร์ฟเวอร์รัน SCLK ที่ความถี่ 30 MHz ดังนั้น tCYCLE = 33 ns

tSETUP_MARGIN = 33 ns − 1 ns – 5 ns – 7 ns – 11 ns – 7 ns = 2 ns

tHOLD_MARGIN =11 ns + 7 ns + 7 ns – 1 ns – 2 ns = 22 ns

ทั้งแอมพลิจูดของการตั้งค่าและการคงค่าเป็นบวก ดังนั้น SPI SCLK จึงสามารถทำงานที่ความถี่ 30 MHz ได้

คุณภาพสัญญาณดิจิตอล

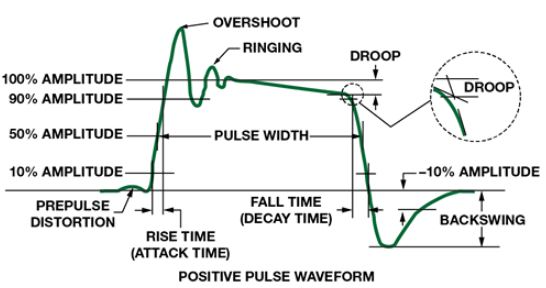

ความสมบูรณ์ของสัญญาณดิจิทัล ซึ่งรวมถึงจังหวะเวลาและคุณภาพของสัญญาณ ช่วยให้มั่นใจได้ว่าสัญญาณต่างๆ จะได้รับในระดับแรงดันไฟฟ้าที่กำหนด ไม่รบกวนซึ่งกันและกัน ไม่ทำให้อุปกรณ์อื่นเสียหาย และไม่ก่อให้เกิดมลภาวะทางคลื่นแม่เหล็กไฟฟ้า คุณภาพของสัญญาณถูกกำหนดด้วยคำศัพท์หลายคำ ดังแสดงในรูปที่ 5 หัวข้อนี้จะแนะนำเกี่ยวกับแรงดันไฟฟ้าเกิน สัญญาณริงกิ้ง สัญญาณสะท้อน และสัญญาณครอสทอล์ค

การสะท้อนเป็นผลมาจากความไม่ตรงกันของอิมพีแดนซ์ ขณะที่สัญญาณเดินทางผ่านสายส่ง อิมพีแดนซ์จะเปลี่ยนแปลงทันทีที่แต่ละอินเทอร์เฟซ สัญญาณบางส่วนจะสะท้อนกลับ และบางส่วนจะถูกส่งต่อไปตามสายส่ง การสะท้อนอาจทำให้เกิดสัญญาณเกิน สัญญาณต่ำ เสียงริง และขอบสัญญาณนาฬิกาที่ไม่เป็นเอกภาพ (non-monotonic clock edge) ที่เครื่องรับ

แรงดันไฟฟ้าเกินและแรงดันไฟฟ้าต่ำเกินไปอาจทำให้วงจรป้องกันอินพุตเสียหายหรือทำให้อายุการใช้งานของไอซีสั้นลง รูปที่ 6 แสดงค่าพิกัดสูงสุดสัมบูรณ์ของ AD7606 แรงดันไฟฟ้าอินพุตดิจิทัลต้องอยู่ระหว่าง –0.3 V และ VDRIVE +0.3 V นอกจากนี้ การส่งเสียงกริ่งเกินค่า VIL สูงสุดหรือต่ำกว่าค่า VIH ต่ำสุดอาจทำให้เกิดข้อผิดพลาดทางตรรกะได้

เพื่อลดการสะท้อนแสง:

- ทำให้รอยตามสั้นที่สุดเท่าที่จะเป็นไปได้

- ควบคุมค่าอิมพีแดนซ์ลักษณะเฉพาะของรอย

- เอาส่วนที่เหลือออก

- ใช้โปรแกรมยุติการใช้งานที่เหมาะสม

- ใช้โลหะแข็งที่มีพื้นที่วงเล็กเป็นระนาบอ้างอิงกระแสกลับ

- ใช้กระแสไดรฟ์ที่ต่ำกว่าและความเร็วที่แปรผัน

มีเครื่องมือซอฟต์แวร์หรือเว็บไซต์มากมายที่สามารถใช้คำนวณค่าอิมพีแดนซ์ลักษณะเฉพาะของเส้นสัญญาณได้ เช่น Si9000 PCB Line Field Solver ของ Polar Instruments เครื่องมือเหล่านี้ช่วยให้การคำนวณค่าอิมพีแดนซ์ลักษณะเฉพาะเป็นเรื่องง่าย โดยการเลือกแบบจำลองสายส่งและตั้งค่าพารามิเตอร์ต่างๆ เช่น ประเภทและความหนาของฉนวนไฟฟ้า ความกว้างของเส้นสัญญาณ ความหนา และระยะห่างของเส้นสัญญาณ

IBIS เป็นมาตรฐานใหม่ที่ใช้อธิบายพฤติกรรมแบบอะนาล็อกของ I/O ดิจิทัลของไอซี ADI มีแบบจำลอง IBIS สำหรับ SAR ADC การจำลองแบบก่อนการวางผังจะตรวจสอบการกระจายสัญญาณนาฬิกา ประเภทแพ็คเกจชิป การจัดวางบอร์ด โทโพโลยีเครือข่าย และกลยุทธ์การสิ้นสุด นอกจากนี้ยังสามารถตรวจสอบข้อจำกัดด้านเวลาของอินเทอร์เฟซแบบอนุกรมเพื่อกำหนดตำแหน่งและการจัดวาง การจำลองหลังการวางผังจะตรวจสอบว่าการออกแบบเป็นไปตามแนวทางและข้อจำกัดทั้งหมด และตรวจสอบการละเมิด เช่น การสะท้อนแสง ความถี่สัญญาณรบกวน และสัญญาณรบกวนข้ามสัญญาณ

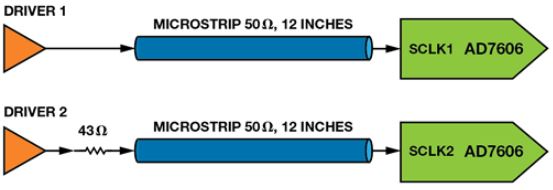

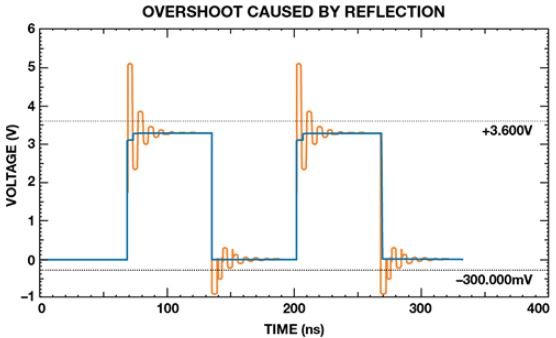

รูปที่ 7 แสดงไดรเวอร์ตัวหนึ่งที่เชื่อมต่อกับ SCLK1 ผ่านสาย IC 12Ω และไดรเวอร์ตัวที่สองที่เชื่อมต่อกับ SCLK2 ผ่านตัวต้านทาน 43Ω แบบอนุกรมกับ IC

รูปที่ 8 แสดงให้เห็นการโอเวอร์ชู้ตครั้งใหญ่บน SCLK1 ซึ่งละเมิดค่าพิกัดสูงสุดสัมบูรณ์จาก -0.3 V ถึง +3.6 V ตัวต้านทานแบบอนุกรมจะลดอัตราการเปลี่ยนแปลงบน SCLK2 ทำให้สัญญาณอยู่ในเกณฑ์มาตรฐาน

ครอสทอล์ค (Crosstalk) คือการเชื่อมโยงพลังงานระหว่างสายส่งขนานผ่านความจุร่วม (สนามไฟฟ้า) หรือความเหนี่ยวนำร่วม (สนามแม่เหล็ก) ปริมาณครอสทอล์คขึ้นอยู่กับเวลาขึ้นของสัญญาณ ความยาวของสายส่งขนาน และระยะห่างระหว่างสายส่ง

มาตรการทั่วไปบางประการในการควบคุมการสนทนาข้ามกัน ได้แก่:

- เพิ่มระยะห่างระหว่างบรรทัด

- ลดการทำงานแบบขนานให้เหลือน้อยที่สุด

- เก็บร่องรอยไว้ใกล้กับระนาบโลหะอ้างอิง

- ใช้โปรแกรมยุติการใช้งานที่เหมาะสม

- ชะลออัตราการเปลี่ยนแปลงของสัญญาณ

ประสิทธิภาพการทำงานลดลงอันเนื่องมาจากการดำเนินการแบบดิจิทัล

การทำงานแบบดิจิทัลสามารถลดประสิทธิภาพของ SAR ADC โดย SNR ลดลงเนื่องจากสัญญาณไฟฟ้าดิจิทัลหรือกราวด์ สัญญาณรบกวนจากนาฬิกาการสุ่มตัวอย่าง และสัญญาณรบกวนจากสัญญาณดิจิทัล

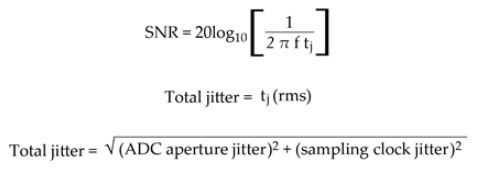

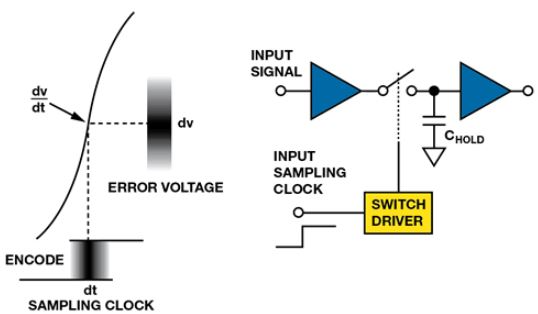

ความสั่นไหวของช่องรับแสงหรือความสั่นไหวของสัญญาณนาฬิกาการสุ่มตัวอย่าง (sampling clock jitter) เป็นตัวจำกัดค่า SNR โดยเฉพาะอย่างยิ่งสำหรับสัญญาณอินพุตความถี่สูง ความสั่นไหวของระบบเกิดจากสองแหล่ง ได้แก่ ความสั่นไหวของช่องรับแสงจากวงจรติดตามและคงสัญญาณบนชิป (ความสั่นไหวภายใน) และความสั่นไหวจากสัญญาณนาฬิกาการสุ่มตัวอย่าง (ความสั่นไหวภายนอก) ความสั่นไหวของช่องรับแสงคือความแปรผันของเวลาการสุ่มตัวอย่างระหว่างการแปลงสัญญาณ และเป็นฟังก์ชันหนึ่งของ ADC ความสั่นไหวของสัญญาณนาฬิกาการสุ่มตัวอย่างมักเป็นแหล่งที่มาหลักของความคลาดเคลื่อน แต่ทั้งสองแหล่งนี้ทำให้เกิดความแปรผันของเวลาการสุ่มตัวอย่างสัญญาณอินพุตอะนาล็อก ดังแสดงในรูปที่ 9 ผลกระทบของทั้งสองแหล่งนี้ไม่สามารถแยกแยะได้

สัญญาณรบกวนโดยรวมสร้างแรงดันไฟฟ้าผิดพลาด โดยที่ SNR โดยรวมของ ADC ถูกจำกัดด้วย

โดยที่ f คือความถี่อินพุตแอนะล็อกและ tj คือจิตเตอร์ของสัญญาณนาฬิกาโดยรวม

ตัวอย่างเช่น ด้วยอินพุตแอนะล็อก 10 kHz และสัญญาณรบกวนรวม 1 ns SNR จะถูกจำกัดที่ 84 dB

สัญญาณรบกวนจากแหล่งจ่ายไฟจากการสลับเอาต์พุตดิจิทัลต้องแยกออกจากแหล่งจ่ายไฟอนาล็อกที่ละเอียดอ่อน แยกแหล่งจ่ายไฟอนาล็อกและดิจิทัลออกจากกัน โดยใส่ใจเส้นทางกระแสไฟฟ้ากลับลงกราวด์อย่างระมัดระวัง

ADC SAR ความแม่นยำสูงอาจมีความไวต่อกิจกรรมบนอินเทอร์เฟซดิจิทัล แม้ว่าแหล่งจ่ายไฟจะถูกแยกและแยกออกจากกันอย่างเหมาะสม สัญญาณนาฬิกาแบบเบิร์สต์มักจะมีประสิทธิภาพดีกว่าสัญญาณนาฬิกาแบบต่อเนื่อง เอกสารข้อมูลมักระบุช่วงเวลาที่เงียบซึ่งอินเทอร์เฟซไม่ควรทำงาน การลดกิจกรรมดิจิทัลในช่วงเวลาดังกล่าวให้เหลือน้อยที่สุด ซึ่งโดยทั่วไปคือระหว่างการสุ่มตัวอย่างและเมื่อมีการตัดสินใจบิตที่สำคัญ อาจเป็นเรื่องท้าทายสำหรับอัตราทรูพุตที่สูงขึ้น

บทสรุป

ให้ความสำคัญกับการแปลงข้อมูลเป็นดิจิทัลเพื่อให้มั่นใจว่าการแปลงข้อมูลจาก SAR ADC ถูกต้อง ข้อผิดพลาดในการแปลงข้อมูลเป็นดิจิทัลอาจทำให้ SAR ADC เข้าสู่สถานะที่ไม่รู้จัก ส่งผลให้เกิดการทำงานผิดพลาดหรือประสิทธิภาพลดลง บทความนี้จะช่วยให้นักออกแบบค้นหาสาเหตุที่แท้จริงและนำเสนอวิธีแก้ไข

ผลิตภัณฑ์

October 1, 2025

ออกแบบอินเทอร์เฟซดิจิทัลที่เชื่อถือได้สำหรับ ADC แบบประมาณค่าต่อเนื่อง

บทความนี้ควรช่วยให้นักออกแบบตรวจสอบสาเหตุหลักและเสนอวิธีแก้ไข

by

นักเขียนบทความ