ผลิตภัณฑ์

19

Jan

ทำความเข้าใจเกี่ยวกับการจัดการความร้อนของอุปกรณ์ GaN ระดับชิป

บทความนี้กล่าวถึงความท้าทายที่การจัดการความร้อนเกิดขึ้นเนื่องจากความหนาแน่นของพลังงานที่เพิ่มขึ้น โดยเฉพาะอย่างยิ่งกับบรรจุภัณฑ์ขนาดเศษ

เซมิคอนดักเตอร์กําลังแบนด์แกปกว้าง (WBG) กําลังถูกนํามาใช้ในการออกแบบกระแสหลักเนื่องจากการปรับปรุงลําดับความสําคัญของตัวเลขคุณธรรมทางไฟฟ้า (FOM) การปรับปรุงประสิทธิภาพครั้งใหญ่เหล่านี้ จําเป็นต้องทบทวนสมมติฐานการออกแบบหลายอย่าง รวมถึงการจัดการความร้อน [1]

บทความนี้กล่าวถึงความท้าทายที่การจัดการความร้อนเกิดขึ้นเนื่องจากความหนาแน่นของพลังงานที่เพิ่มขึ้น โดยเฉพาะอย่างยิ่งกับบรรจุภัณฑ์ขนาดเศษ (CSP) อย่างไรก็ตาม สิ่งที่บางครั้งถูกมองข้ามก็คือ FET พลังงาน CSP eGaN® และวงจรรวมมีประสิทธิภาพการระบายความร้อนที่ยอดเยี่ยมเมื่อติดตั้งบนแผงวงจรพิมพ์มาตรฐาน (PCB) ด้วยวิธีการง่ายๆ ในการติดฮีตซิงก์

ตัวอย่างเช่น CSP GaN FET ที่มีขนาด 4 มม.2 บน PCB 4 ชั้นมาตรฐานสามารถบรรลุค่าความต้านทานความร้อนแบบแยกถึงฮีทซิงก์ที่น้อยกว่า 4 K/W ด้วยวัสดุและเทคนิคการประกอบและฮีตซิงก์ต้นทุนต่ํา การวิเคราะห์ การจําลอง และการตรวจสอบการทดลองมีให้ในบทความนี้ นอกจากนี้ยังมีการกล่าวถึงเส้นทางสู่การปรับปรุงความร้อนเพิ่มเติม

ตัวอย่างเช่นพิจารณากรณีของวงจรเรียงกระแสแบบซิงโครนัสตัวแปลงบั๊กที่ติดตั้งบนพื้นผิวซึ่งการสูญเสียที่โดดเด่นคือการสูญเสียการนําไฟฟ้า CSP eGaN FET ซึ่งเป็น EPC2059 ใช้พื้นที่ PCB 3.92 มม. 2 สําหรับ FET 170V, 9 mΩ ในขณะที่ Si MOSFET ระบายความร้อนสองด้าน 150V, 16.5 mΩ ที่ล้ําสมัยใช้พื้นที่ PCB ของบอร์ดเกือบแปดเท่าที่ 30.9 มม. 2

หากพื้นที่รอยเท้าเป็นปัจจัยสําคัญที่กําหนดอุณหภูมิที่เพิ่มขึ้น Si MOSFET ที่ใหญ่กว่าจะมีอุณหภูมิเพิ่มขึ้นประมาณ 23% ของ GaN สําหรับกระแสที่กําหนด แม้ว่า eGaN FET จะมีความต้านทานต่อการเปิด (RDS(on)) ที่ต่ํากว่ามากก็ตาม อย่างไรก็ตาม ในทางปฏิบัติ ประสิทธิภาพการระบายความร้อนของ CSP eGaN FET ดูเหมือนจะเทียบเท่าหรือดีกว่า Si MOSFET ที่ใหญ่กว่า ผลลัพธ์ที่ดูเหมือนขัดกับสัญชาตญาณนี้และเหตุผลนั้นไม่ชัดเจนดังนั้นจึงจําเป็นต้องมีการตรวจสอบเชิงลึก

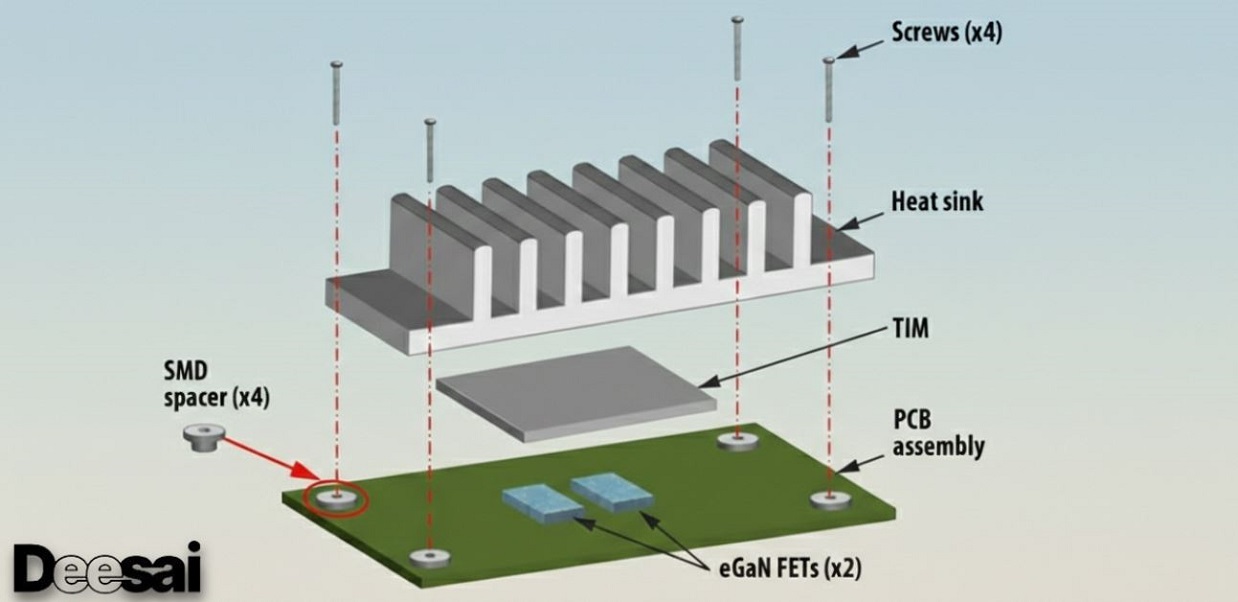

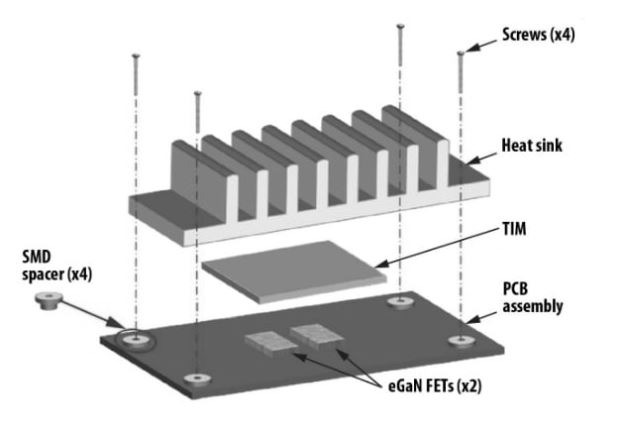

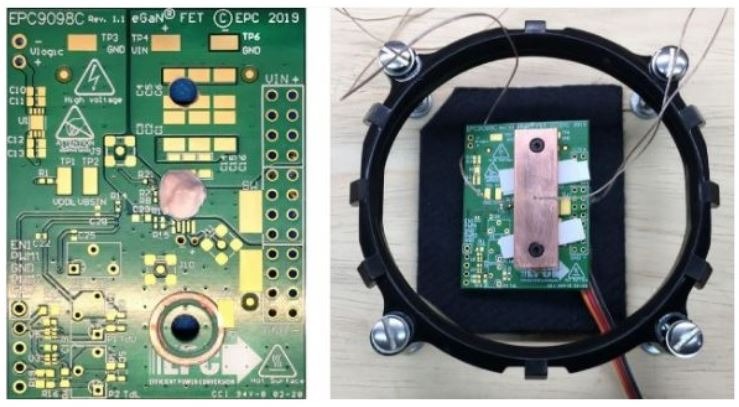

สิ่งพิมพ์หลายฉบับแสดงให้เห็นว่า eGaN FET ระดับชิปมีประสิทธิภาพการระบายความร้อนสัมบูรณ์ที่ยอดเยี่ยม แม้ว่าจะมีพื้นที่เล็กกว่ามากเมื่อเทียบกับ MOSFET RDS(on) ที่เทียบเท่ากัน และมีวิธีการติดตั้งฮีตซิงก์ที่ใช้งานได้จริง [2, 3] ดังที่แสดงในรูปที่ 1 ที่แสดงวิธีการง่ายๆ ในการติดฮีตซิงก์เข้ากับ CSP eGaN FET น่าเสียดายที่สิ่งพิมพ์ส่วนใหญ่ให้รายละเอียดเพียงเล็กน้อยเกี่ยวกับการไหลของความร้อนและแบบจําลองความร้อนเมื่อมี บทความมีความเรียบง่ายและมีเหตุผลที่เข้มงวดเพียงเล็กน้อย

เนื่องจากอุณหภูมิทางแยกสูงสุด Tj,max มักเป็นปัจจัยจํากัดหลักในการออกแบบ จึงเป็นสิ่งสําคัญสําหรับนักออกแบบระบบไฟฟ้าที่จะต้องเข้าใจว่าสามารถบรรลุประสิทธิภาพการระบายความร้อนสูงได้อย่างไรและทําไม ความเข้าใจดังกล่าวให้ความมั่นใจในการออกแบบ ดังนั้นทําให้รอบการออกแบบสั้นลงลดปริมาณและความรุนแรงของการทดสอบที่จําเป็นเพิ่มความน่าเชื่อถือและลดต้นทุนโดยรวม

ในการออกแบบจํานวนมากที่ใช้เซมิคอนดักเตอร์กําลังแบบติดตั้งบนพื้นผิว PCB และอินเทอร์เฟซทรานซิสเตอร์กับฮีตซิงก์เป็นคอขวดแรกในการไหลของความร้อน [4] ในกรณีที่ใช้ฮีตซิงก์บทบาทของ PCB ในการกระจายความร้อนมักถูกละเลย แต่ในความเป็นจริงแล้วเป็นเส้นทางสําคัญสําหรับการไหลของความร้อน การมีส่วนร่วมของ PCB ในการสกัดความร้อนมีความสําคัญแม้กระทั่งสําหรับ CSP eGaN FET ที่มีขนาดเล็กมาก ซึ่งในการออกแบบที่ใช้งานได้จริง FET ดังกล่าวสามารถบรรลุประสิทธิภาพการระบายความร้อนจากทางแยกถึงสภาพแวดล้อมเทียบเท่าหรือดีกว่า Si MOSFET ที่ใหญ่กว่ามาก

เมื่อรวมกับประสิทธิภาพทางไฟฟ้าที่เหนือกว่าของ eGaN FET จะสามารถลดขนาด ระดับพลังงานเพิ่มขึ้น และอุณหภูมิในการทํางานลดลง สิ่งนี้สามารถแสดงได้โดยใช้การจําลององค์ประกอบ 3 มิติโดยละเอียดของเค้าโครง PCB ทั่วไปร่วมกับการตรวจสอบการทดลอง

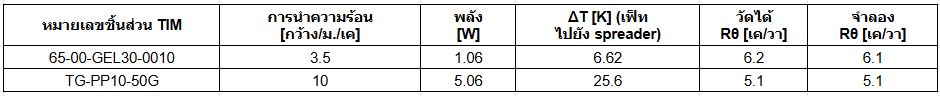

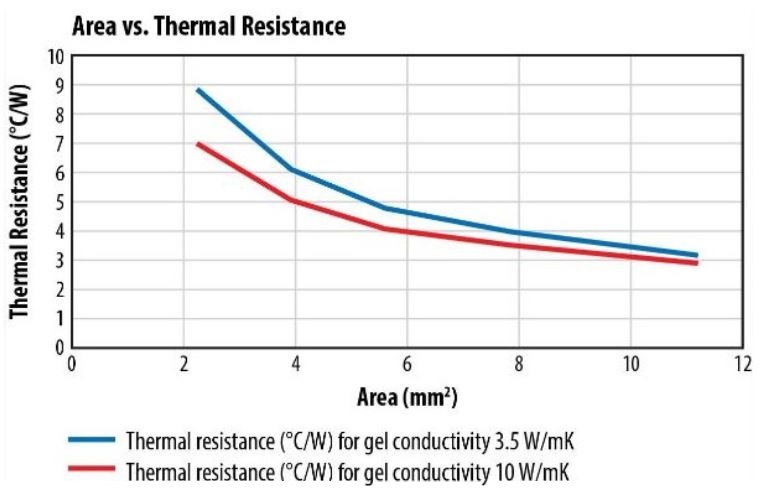

สําหรับการใช้งานที่ใช้พลังงานสูงหรือการใช้งานในสภาพแวดล้อมที่มีอุณหภูมิแวดล้อมสูงฮีตซิงก์จะใช้เพื่อถ่ายเทพลังงานความร้อนไปยังสภาพแวดล้อมโดยรอบ แนวทางการจัดการความร้อนทั่วไปสําหรับ CSP eGaN FET เกี่ยวข้องกับการใช้วัสดุเชื่อมต่อความร้อนที่เป็นฉนวนไฟฟ้า (TIM) กับพื้นผิวด้านบนของ FET ที่ติดตั้ง และติดฮีตซิงก์ไว้ด้านบนด้วยกลไก ในการกําหนดค่านี้ มักใช้ตัวเว้นวรรคเพื่อให้แน่ใจว่าฮีตซิงก์มีระยะห่างเพียงพอจากพื้นผิวด้านบนของ FET ถึงพื้นผิวที่หันหน้าเข้าหากันของฮีตซิงก์ เพื่อให้เป็นไปตามข้อกําหนดของแรงดันไฟฟ้าและดูดซับความแปรผันทางกล ดังแสดงในรูปที่ 1

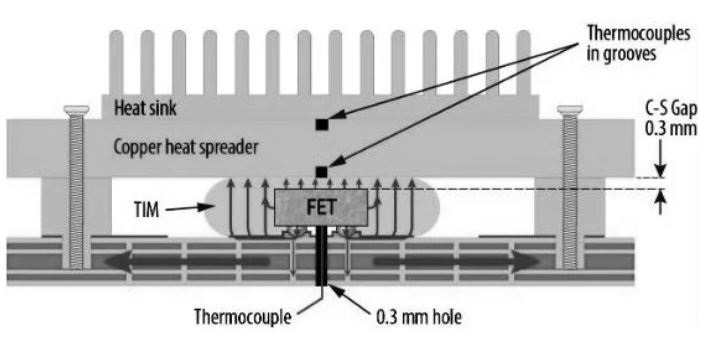

รูปที่ 2 แสดงเส้นทางการไหลของความร้อนต่างๆ สําหรับชุดระบายความร้อนที่อธิบายไว้ก่อนหน้านี้ โดยสัญชาตญาณดูเหมือนว่าการไหลของความร้อนจากด้านบนและด้านข้างของ FET ระดับชิปมีอิทธิพลเหนือกว่าเนื่องจากเส้นทางสั้น ๆ ผ่าน TIM ในขณะที่ในความเป็นจริงการไหลของความร้อนตามเส้นทางฮีตซิงก์ PCBTIM ก็มีส่วนสําคัญในการกําจัดความร้อนเช่นกัน

เนื่องจากพันธะโลหะบัดกรี FET จึงมีการเชื่อมต่อทางความร้อนที่ดีเยี่ยมกับทองแดงบน PCB PCB กระจายความร้อนได้อย่างมีประสิทธิภาพเนื่องจากค่าการนําความร้อนของทองแดงสูงกว่า TIM ประมาณสองลําดับความสําคัญ แม้ว่าความร้อนจาก PCB ไปยังฮีตซิงก์จะต้องไหลผ่านความหนาของ TIM ที่ใหญ่กว่าเส้นทางจาก FET ไปยังฮีตซิงก์ 2-5 เท่า แต่หน้าตัดที่มีประสิทธิภาพของ TIM ในเส้นทางนี้อาจมากกว่า 10 เท่าของพื้นที่ผิวที่สัมผัสของ FET เนื่องจากพื้นที่ของมันเป็นสัดส่วนกับกําลังสองของรัศมีของกระบอกสูบที่เกิดจากการใช้วัสดุส่วนต่อประสานความร้อน ดังนั้นจึงต้องคํานึงถึงการมีส่วนร่วมของเส้นทางระบายความร้อนของ PCB-to-heat sink เมื่อวิเคราะห์แนวทางการจัดการความร้อนนี้

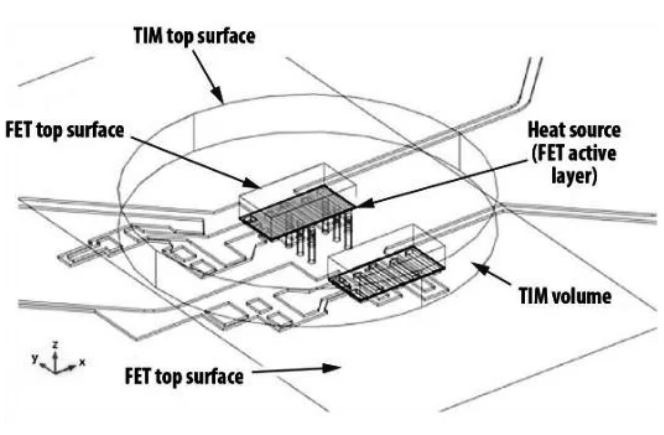

การวิเคราะห์ข้างต้นสามารถทําได้โดยใช้เครื่องมือวิธีไฟไนต์เอลิเมนต์ 3 มิติ (FEM) PCB แบบฮาล์ฟบริดจ์สําหรับ eGaN FET สร้างกรณีพื้นฐาน PCB นี้มีเลย์เอาต์ที่ปรับให้เหมาะสมเพื่อประสิทธิภาพทางไฟฟ้าที่ดีที่สุด [5] และใช้โครงสร้างฟอยล์ทองแดง 4 มม. 70 มม. อิเล็กทริก FR408 และมีความหนารวม 1.6 มม. (62 มิล) ปริมาตรของสีโป๊วนําความร้อนวางอยู่บน FET ที่ติดตั้งและบริเวณใกล้เคียงดังแสดงในรูปที่ 3 ฮีตซิงก์วางอยู่เหนือ FET โดยมีช่องว่างระหว่างด้านบนของ FET กับพื้นผิวฮีตซิงก์ บอร์ดมีทองแดงเทพร้อมช่องว่างฉนวนและชุดย่อยของจุดแวะที่จะใช้ในการออกแบบทั่วไป ประเด็นสําคัญคือประสิทธิภาพทางไฟฟ้าที่ดีที่สุดจะผลักดันให้นักออกแบบใส่ทองแดงในบริเวณใกล้เคียงกับ FET ให้ได้มากที่สุด ซึ่งยังเป็นประโยชน์ต่อประสิทธิภาพการระบายความร้อนอีกด้วย

ผลการทดลอง มีการทดลองทางกายภาพหลายชุดเพื่อตรวจสอบการจําลองเหล่านี้และเพื่อทําความเข้าใจเพิ่มเติมเกี่ยวกับผลกระทบในทางปฏิบัติต่อ FET เช่น อิมพีแดนซ์การสัมผัสความร้อน ความเห็นพ้องต้องกันที่ดีระหว่างผลลัพธ์เชิงประจักษ์และการจําลอง ซึ่งสนับสนุนความเชื่อมั่นในการจําลอง

การวิเคราะห์ต้นทุนทําด้วยวัสดุ 10 W/m/K (TGPP10-50G) ที่มีราคาแพงกว่า กระบอกสูบขนาดเส้นผ่านศูนย์กลาง 10 มม. ของวัสดุรอบ FET มีปริมาตรประมาณ 70 มล. สําหรับอัตราการผลิตปานกลาง ต้นทุน TIM ต่อ FET จะน้อยกว่า 0.01 ดอลลาร์สหรัฐฯ

สรุป

eGaN FET ขนาดเล็กมีประสิทธิภาพการระบายความร้อนที่ยอดเยี่ยมเมื่อติดตั้งบน PCB ที่ออกแบบมาเพื่อประสิทธิภาพทางไฟฟ้าที่ดีที่สุด ประสิทธิภาพนี้ได้มาจากโซลูชันระบายความร้อนที่เรียบง่าย ผลิตได้ และคุ้มค่า

ผลิตภัณฑ์

February 23, 2026

ทำความเข้าใจเกี่ยวกับการจัดการความร้อนของอุปกรณ์ GaN ระดับชิป

บทความนี้กล่าวถึงความท้าทายที่การจัดการความร้อนเกิดขึ้นเนื่องจากความหนาแน่นของพลังงานที่เพิ่มขึ้น โดยเฉพาะอย่างยิ่งกับบรรจุภัณฑ์ขนาดเศษ

by

นักเขียนบทความ