ผลิตภัณฑ์

19

Jan

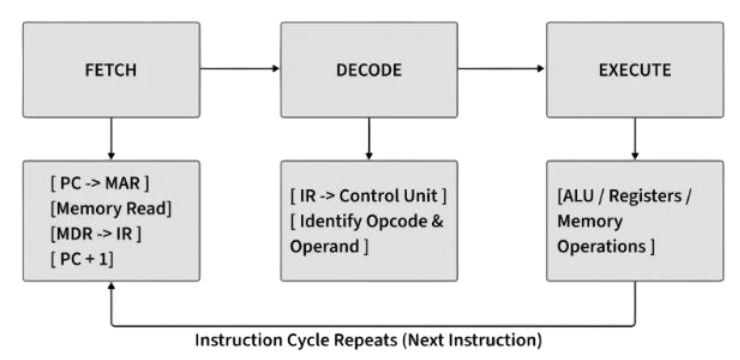

วงจรการทำงานของคำสั่งหลัก

ค้นพบวิธีที่โปรเซสเซอร์ของคุณดึงข้อมูล ถอดรหัส และดําเนินการทุกคําสั่งในพริบตา

วงจรคําสั่งเป็นกระบวนการปฏิบัติงานพื้นฐานของ CPU ของคอมพิวเตอร์ โดยอ้างถึงลําดับของขั้นตอนที่ตามมาเพื่อดึงข้อมูล ถอดรหัส และดําเนินการคําสั่งระดับเครื่องแต่ละรายการ วงจรนี้เกิดขึ้นหลายล้านหรือหลายพันล้านครั้งต่อวินาที เพื่อให้มั่นใจได้ถึงการดําเนินการที่เหมาะสมและการทํางานของระบบที่ราบรื่น

- ตรวจสอบให้แน่ใจว่าคําสั่งได้รับการประมวลผลอย่างชัดเจนและเป็นระเบียบ

- CPU ดึงข้อมูล ถอดรหัส และดําเนินการคําสั่งเพื่อทํางานอย่างต่อเนื่อง

การลงทะเบียนคีย์ที่ใช้ในรอบการเรียนการสอน

การลงทะเบียนหลายตัวภายใน CPU มีส่วนร่วมอย่างแข็งขันในการดําเนินการตามรอบคําสั่ง:

- ตัวนับโปรแกรม (PC):เก็บที่อยู่ของคําสั่งถัดไปที่จะดําเนินการ เพิ่มขึ้นโดยอัตโนมัติหลังจากดึงข้อมูลคําสั่ง

- การลงทะเบียนคําสั่ง (IR): เก็บคําสั่งที่กําลังดําเนินการอยู่

- การลงทะเบียนที่อยู่หน่วยความจํา (MAR) (อุปกรณ์เสริม): เก็บที่อยู่ของตําแหน่งหน่วยความจําที่กําลังเข้าถึง

- การลงทะเบียนข้อมูลหน่วยความจํา (MDR) (อุปกรณ์เสริม): เก็บข้อมูลที่อ่านจากหรือเขียนลงในหน่วยความจํา

รอบการดึงข้อมูล

รอบการดึงข้อมูลเป็นขั้นตอนแรกในวงจรการเรียนการสอน ที่นี่ CPU จะดึงคําสั่งจากหน่วยความจําโดยใช้ตัวนับโปรแกรม (PC)

ขั้นตอนในรอบการดึงข้อมูล:

- ที่อยู่ในพีซีจะถูกโอนไปยัง MAR

- ชุดควบคุมส่งสัญญาณอ่านไปยังหน่วยความจํา

- คําสั่งที่แอดเดรสหน่วยความจํานั้นจะถูกวางไว้ใน MDR

- เนื้อหา MDR จะถูกถ่ายโอนไปยัง IR

- พีซีจะเพิ่มขึ้นเพื่อชี้ไปยังคําสั่งถัดไป

ตัวอย่าง:

คําแนะนํา: โหลด 500

พีซี = 100

หน่วยความจํา IR ←[100]

พีซี ← พีซี + 1

หลังจากรอบนี้ IR จะมีคําสั่ง LOAD 500 ตอนนี้พีซีชี้ไปที่คําสั่งถัดไป

วงจรถอดรหัส

ในรอบการถอดรหัส ชุดควบคุมจะตีความคําสั่งที่ดึงมาซึ่งจัดเก็บไว้ใน IR

ขั้นตอนในวงจรถอดรหัส:

- ชุดควบคุมตรวจสอบส่วน opcode ของคําสั่ง

- กําหนดการดําเนินการที่จะดําเนินการ

- ระบุตัวถูกดําเนินการหรือรีจิสเตอร์ที่เกี่ยวข้อง

ตัวอย่าง:

IR = โหลด 500

หน่วยควบคุม:

Opcode = โหลด

ตัวถูกดําเนินการ = 500

ที่นี่ LOAD บ่งบอกถึงการทํางาน 500 คือที่อยู่ของข้อมูลที่จะโหลด

ดําเนินการวงจร

สุดท้าย Execute Cycle จะดําเนินการจริงที่กําหนดในระหว่างขั้นตอนการถอดรหัส

ขั้นตอนในวงจรการดําเนินการ:

- CPU จะดําเนินการขึ้นอยู่กับ opcode

- ดําเนินการทางคณิตศาสตร์หรือตรรกะผ่าน ALU

- ถ่ายโอนข้อมูลระหว่างหน่วยความจําและรีจิสเตอร์

- เปลี่ยนลําดับการดําเนินการ (เช่น คําแนะนําในการกระโดด)

ตัวอย่าง:

โหลด 500

หน่วยความจํา←สะสม[500]

หลังจากดําเนินการวงจรสามารถเริ่มต้นอีกครั้งด้วยคําสั่งถัดไป

ความท้าทายในการดําเนินการคําสั่ง CPU สมัยใหม่

แม้ว่าวงจร Fetch–Decode–Execute จะเป็นรากฐานของการทํางานของ CPU แต่โปรเซสเซอร์สมัยใหม่ต้องเผชิญกับความท้าทายหลายประการเมื่อดําเนินการหลายคําสั่งอย่างมีประสิทธิภาพ ปัญหาเหล่านี้อาจส่งผลต่อประสิทธิภาพ ปริมาณงาน และประสิทธิภาพของระบบโดยรวม

1. อันตรายจากท่อ

Pipelining เป็นเทคนิคที่ใช้ในการปรับปรุงปริมาณงานคําสั่งโดยการทับซ้อนกันการดําเนินการหลายคําสั่ง

อย่างไรก็ตาม อันตรายจากท่อส่งจะเกิดขึ้นเมื่อ:

- คําสั่งหนึ่งขึ้นอยู่กับผลลัพธ์ของคําสั่งก่อนหน้า

- มีการเปลี่ยนแปลงโฟลว์การควบคุม (เช่น สาขา)

- ทรัพยากรฮาร์ดแวร์ไม่พร้อมใช้งานสําหรับขั้นตอนไปป์ไลน์ทั้งหมด

สิ่งนี้นําไปสู่การหยุดชะงักหรือฟองอากาศในท่อส่ง ซึ่งทําให้ประสิทธิภาพลดลงในที่สุด

2. ข้อผิดพลาดในการคาดการณ์สาขา

การคาดการณ์สาขาช่วยให้ CPU คาดเดาผลลัพธ์ของคําสั่งสาขาแบบมีเงื่อนไขเพื่อให้ไปป์ไลน์ทํางานได้อย่างราบรื่น

แต่ถ้าการคาดการณ์ไม่ถูกต้องโปรเซสเซอร์จะต้อง:

- ล้างคําแนะนําที่ไม่ถูกต้องออกจากท่อ

- ดึงเส้นทางคําสั่งที่ถูกต้อง

ส่งผลให้วงจรสูญเปล่าและประสิทธิภาพการดําเนินการลดลง

3. แคชคําสั่งพลาด

แคชคําสั่งเป็นหน่วยความจําความเร็วสูงขนาดเล็กที่ใช้ในการจัดเก็บคําสั่งที่เข้าถึงบ่อย

เมื่อไม่พบคําแนะนําที่จําเป็นในแคช:

- ต้องดึงมาจากหน่วยความจําหลักซึ่งช้ากว่า

- สิ่งนี้นําไปสู่ความล่าช้าและท่อส่งหยุดชะงัก

อัตราการพลาดแคชที่สูงอาจทําให้ประสิทธิภาพของ CPU ลดลงอย่างมาก

4. ข้อจํากัดของ Instruction-Level Parallelism (ILP)

Instruction-Level Parallelism ช่วยให้ CPU สามารถดําเนินการหลายคําสั่งพร้อมกันได้

อย่างไรก็ตาม:

- คําสั่งบางคําสั่งไม่ได้เป็นอิสระหรือขนานกันได้

- การพึ่งพาข้อมูลและโฟลว์การควบคุมมักจะจํากัดการดําเนินการแบบขนาน

ด้วยเหตุนี้ ILP จึงมีข้อจํากัดในทางปฏิบัติ ซึ่งนอกเหนือจากการเพิ่มฮาร์ดแวร์เพิ่มเติมจะไม่ให้การเร่งความเร็วอย่างมีนัยสําคัญ

5. การแย่งชิงทรัพยากร

เมื่อคําสั่งหลายคําสั่ง compete สําหรับทรัพยากร CPU เดียวกัน (เช่น รีจิสเตอร์ พอร์ตหน่วยความจํา หน่วย ALU):

- การดําเนินการต้องรอจนกว่าทรัพยากรจะพร้อมใช้งาน

- สิ่งนี้สร้างปัญหาคอขวดและทําให้ไปป์ไลน์ช้าลง

การจัดกําหนดการทรัพยากรและการออกแบบฮาร์ดแวร์ที่มีประสิทธิภาพช่วยลดปัญหานี้ให้เหลือน้อยที่สุด

ผลิตภัณฑ์

March 12, 2026

วงจรการทำงานของคำสั่งหลัก

ค้นพบวิธีที่โปรเซสเซอร์ของคุณดึงข้อมูล ถอดรหัส และดําเนินการทุกคําสั่งในพริบตา

by

นักเขียนบทความ