ผลิตภัณฑ์

19

Jan

การออกแบบ IC พลังงานต่ำ: เทคนิคและแนวทางปฏิบัติที่ดีที่สุด

บทความนี้จะสรุปเทคนิคการออกแบบที่จำเป็นและแนวทางปฏิบัติที่ดีที่สุดสำหรับการใช้งานอย่างมีประสิทธิผล

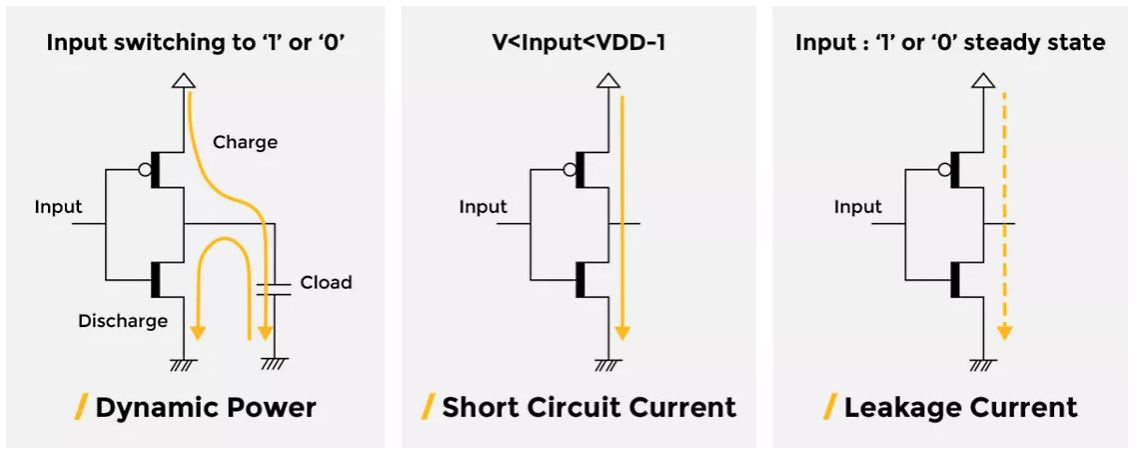

การออกแบบวงจรรวม (IC) กำลังต่ำถือเป็นส่วนสำคัญของอุปกรณ์อิเล็กทรอนิกส์สมัยใหม่ เนื่องจากช่วยให้แบตเตอรี่มีอายุการใช้งานยาวนานขึ้นและลดการใช้พลังงานในอุปกรณ์ต่างๆ ตลาดอุปกรณ์ที่ใช้แบตเตอรี่กำลังเติบโตอย่างรวดเร็วทำให้ผู้ออกแบบชิปต้องพิจารณาเทคนิคต่างๆ อย่างรอบคอบเพื่อลดการใช้พลังงานของ IC มีเทคนิคมากมายที่สามารถนำมาใช้เพื่อลดการใช้พลังงานแบบสถิตและไดนามิกของ IC กระแสไฟฟ้าตรงและกระแสไฟฟ้ารั่วเป็นแหล่งจ่ายพลังงานแบบสถิต ขณะที่พลังงานแบบไดนามิกขึ้นอยู่กับความถี่ ซึ่งมาจากการสลับทรานซิสเตอร์และไฟฟ้าลัดวงจร

เพื่อสร้างการออกแบบที่ประหยัดพลังงาน ผู้ออกแบบจะต้องลดองค์ประกอบพลังงานแต่ละส่วนที่มีส่วนในการใช้พลังงานทั้งหมดให้เหลือน้อยที่สุด รูปที่ 1 แสดงคุณลักษณะพลังงานทั้งแบบไดนามิกและแบบคงที่ การชาร์จแบบไดนามิกของอินเวอร์เตอร์คอมพลีเมนต์เมทัลออกไซด์เซมิคอนดักเตอร์ (CMOS) ทำให้การใช้พลังงานเพิ่มขึ้นตามสัดส่วนความถี่สัญญาณนาฬิกา การรั่วไหลของพลังงานผ่านทรานซิสเตอร์เมื่อไม่ได้ใช้งานถือเป็นพลังงานคงที่

นักออกแบบที่ใช้พลังงานต่ำสามารถลดการใช้พลังงานโดยรวมได้โดยการควบคุมแรงดันไฟฟ้าของแหล่งจ่ายไฟ ลดความซับซ้อนของวงจรและความถี่สัญญาณนาฬิกา และตรวจสอบแหล่งจ่ายกระแสไฟฟ้าตรงและความจุของสวิตช์ ทุกอย่างเชื่อมต่อกัน ดังนั้นนักออกแบบจึงต้องสร้างสมดุลของปัจจัยเหล่านี้ด้วยการทดลองและใช้เทคนิคการออกแบบที่ใช้พลังงานต่ำเพื่อเพิ่มประสิทธิภาพการออกแบบ

เทคนิคและแนวทางปฏิบัติที่ดีที่สุดสำหรับการออกแบบพลังงานต่ำ

ประตูนาฬิกา

วิธีหนึ่งในการลดการใช้พลังงานของอุปกรณ์คือการปรับการออกแบบที่ระดับการถ่ายโอนรีจิสเตอร์ (RTL) ซึ่งเป็นหนึ่งในเทคนิคที่ใช้กันมากที่สุดในการลดการใช้พลังงานแบบไดนามิก ในระดับ RTL พลังงานจะถูกใช้เมื่อทรานซิสเตอร์เปลี่ยนสถานะตรรกะ หรือเมื่อใช้พลังงานเพื่อชาร์จโหลดแบบคาปาซิทีฟ พลังงานแบบไดนามิกทั้งหมดคือ:

โดยที่ CL คือความจุโหลด, C คือความจุภายในชิป, f คือความถี่ในการทำงาน และ N คือจำนวนบิตที่ถูกสลับ สามารถลดกระแสไฟฟ้าที่มีกระแสไฟฟ้าไหลผ่านได้อย่างง่ายดายโดยการปิดสัญญาณนาฬิกาเมื่อไม่จำเป็น แทนที่จะใช้เกต AND/NOR ควรใช้เกตสวิตช์สัญญาณนาฬิกาแบบแลตช์เพื่อหลีกเลี่ยงการใช้พลังงานเพิ่มเติม การปิดสัญญาณนาฬิกาไปยังชิ้นส่วนบางส่วนของไอซีจะช่วยลดการใช้พลังงานได้อย่างมาก เนื่องจากทรานซิสเตอร์ในบริเวณดังกล่าวจะไม่ถูกสลับและใช้พลังงาน

ประตูไฟฟ้า

บล็อกในไอซีไม่ได้ทำงานอย่างต่อเนื่องทั้งหมด ขึ้นอยู่กับการใช้งานในอุปกรณ์ บล็อกไม่จำเป็นต้องมีแหล่งจ่ายไฟหากไม่ได้ทำงานในกรณีใดกรณีหนึ่ง การลดการใช้พลังงานสามารถทำได้โดยการปิดแหล่งจ่ายไฟไปยังบล็อกที่ไม่ได้ใช้งาน เพื่อใช้เทคนิคนี้ได้อย่างมีประสิทธิภาพ นักออกแบบสามารถใช้บล็อกแยกเพื่อป้องกันสัญญาณที่ไม่จำเป็นจากบล็อกแบบเกตไฟฟ้า

เกตความถี่

อย่างที่ทราบกันดีว่าชิปประกอบด้วยบล็อกจำนวนมาก และแต่ละบล็อกไม่จำเป็นต้องใช้ความถี่สูงสุดในการทำงาน เทคนิคที่ดีที่สุดคือการแยกบล็อกตามความต้องการความถี่ และให้สัญญาณนาฬิกาที่แตกต่างกันไปยังแต่ละบล็อก วิธีนี้สามารถลดการใช้พลังงานไดนามิกของไอซีได้อย่างมาก

การออกแบบหลายแรงดันไฟฟ้า

ไม่มีบล็อกใดในการออกแบบที่ต้องการพลังงานเท่ากันในการทำงาน คุณสามารถแบ่งพาร์ติชันชิปตามประสิทธิภาพและความต้องการแรงดันไฟฟ้าของบล็อก ยิ่งความต้องการแรงดันไฟฟ้าสูง การใช้พลังงานก็จะยิ่งสูงขึ้น การสร้างเกาะแรงดันไฟฟ้าที่มีอินพุตแรงดันไฟฟ้าต่างกัน ช่วยลดการใช้พลังงานรวมของไอซีได้อย่างง่ายดาย

อัตราส่วนแรงดันไฟฟ้าและความถี่แบบไดนามิก

เทคนิคการกลับแรงดันมีข้อจำกัดเพียงข้อเดียว คือ เมื่อออกแบบแหล่งจ่ายแรงดันสำหรับบล็อกแล้ว จะไม่สามารถเปลี่ยนแปลงได้ในภายหลัง การควบคุมแรงดันแบบไดนามิกช่วยให้ผู้ออกแบบมีความยืดหยุ่นในการเปลี่ยนแปลงแรงดันในภายหลังตามต้องการ ผู้ออกแบบสามารถตั้งโปรแกรมตัวควบคุมแรงดันเพื่อปรับแหล่งจ่ายไฟไปยังบล็อกต่างๆ ตามการเปลี่ยนแปลงของกระแสไฟฟ้า ในทำนองเดียวกัน การควบคุมแรงดันสามารถใช้ร่วมกับการควบคุมความถี่ ช่วยให้ผู้ออกแบบสามารถปรับเปลี่ยนสัญญาณนาฬิกาที่จ่ายไปยังแต่ละบล็อกได้ด้วยความช่วยเหลือของโปรแกรมซอฟต์แวร์

ลดกำลังการผลิต

เทคนิคการลดพลังงานที่สำคัญที่สุดในปัจจุบันคือการลดแรงดันไฟฟ้าของชิป พลังงานสวิตชิ่งแบบไดนามิกมีบทบาทสำคัญอย่างมากในการออกแบบ finFET และแปรผันตามกำลังสองของแรงดันไฟฟ้า จึงส่งเสริมกระบวนการแรงดันไฟฟ้าต่ำพิเศษ (ULV) อย่างมาก

การแลกเปลี่ยนเพื่อพลังงานรั่วไหล

พลังงานรั่วไหลเป็นปัจจัยสำคัญในการกระจายพลังงานในเทคโนโลยี pre-finFET และสามารถควบคุมได้ดีที่สุดด้วยไลบรารี multi-Vt ไลบรารีเหล่านี้มีสองหรือสามเวอร์ชันต่อเซลล์ แต่ละเวอร์ชันมีการแลกเปลี่ยนประสิทธิภาพ/การรั่วไหลที่แตกต่างกัน ซึ่งช่วยให้นักออกแบบสามารถใช้เซลล์ที่มีการรั่วไหลเร็วในการกำหนดเวลาเส้นทางวิกฤต และใช้เซลล์ที่มีการรั่วไหลต่ำและช้ากว่าในเส้นทางวิกฤตน้อยกว่าได้

โดยรวมแล้ว มีเทคนิคมากมายที่สามารถนำมาใช้เพื่อลดการใช้พลังงานของไอซีได้ การนำเทคนิคเหล่านี้ไปประยุกต์ใช้ควบคู่ไปกับการใช้เครื่องมือออกแบบและจำลองสถานการณ์ที่เหมาะสมจะช่วยให้นักออกแบบสามารถเอาชนะความท้าทายเหล่านี้ได้ เครื่องมืออย่าง Ansys RedHawk-SC ช่วยให้วิศวกรสามารถจำลองและคาดการณ์พฤติกรรมการออกแบบได้ในทุกขั้นตอนของการออกแบบ ช่วยให้คุณสามารถออกแบบไอซีที่ใช้พลังงานต่ำ ประหยัดพลังงานมากขึ้น และมีอายุการใช้งานแบตเตอรี่ที่ยาวนานขึ้น

ความท้าทายในการออกแบบพลังงานต่ำ

- ขอบเขตแรงดันไฟฟ้าตกเริ่มแคบลงมาก โดยเฉพาะอย่างยิ่งกับการออกแบบแรงดันไฟฟ้าต่ำมาก การพัฒนานี้ทำให้การตรวจสอบแรงดันไฟฟ้าตก (IR) เป็นส่วนสำคัญของการออกแบบวงจรรวมสมัยใหม่ทุกประเภท

- แรงดันไฟฟ้าที่ต่ำทำให้เวลาในการส่งสัญญาณไวต่อการเกิดแรงดันตกแบบไดนามิก (DVD) นอกจากนี้ การวิเคราะห์ DVD ที่ครอบคลุมเพียงพอเพื่อบันทึกสถานการณ์การสลับสัญญาณที่อาจเกิดขึ้นได้ทั้งหมดนั้นเป็นเรื่องยาก การวิเคราะห์แรงดันตกอย่างละเอียดเป็นสิ่งสำคัญเพื่อลดผลกระทบของ DVD ต่อเวลาและหลีกเลี่ยงการสูญเสียความถี่เนื่องจากแรงดันตกที่ไม่คาดคิด

- จำเป็นต้องมีการจัดการพื้นที่ที่มีแรงดันไฟฟ้าหลายระดับอย่างระมัดระวัง เพื่อให้มั่นใจว่าการเปลี่ยนผ่านสัญญาณและความสมบูรณ์ของสัญญาณระหว่างพื้นที่แรงดันไฟฟ้าที่แตกต่างกันเป็นไปอย่างเหมาะสม UPF คือมาตรฐานที่ออกแบบมาเพื่อช่วยแก้ไขปัญหานี้

- ประตูไฟฟ้าสร้างปรากฏการณ์การเปลี่ยนผ่านที่ท้าทายทั้งทางไฟฟ้าและทางตรรกะเมื่อเปิดบล็อกอีกครั้ง

- การควบคุมสัญญาณนาฬิกาจะมีประสิทธิภาพสูงสุดเมื่อใช้งานใกล้กับจุดกำเนิดของเครือข่ายการกระจายสัญญาณนาฬิกามากที่สุดเท่าที่จะเป็นไปได้ แต่ข้อจำกัดนี้ถูกจำกัดด้วยความเป็นไปได้ในการจับเวลาสัญญาณทริกเกอร์หากสัญญาณมาถึงตรงเวลา ส่งผลให้เกิดการแลกเปลี่ยนระหว่างประสิทธิภาพการใช้พลังงานที่บรรลุผลและความพยายามในการปรับปรุงการออกแบบให้เหมาะสมที่สุด

ความถูกต้องของการวิเคราะห์กำลังไฟฟ้าใดๆ ขึ้นอยู่กับการทำงานของวงจรเป็นอย่างมาก อย่างไรก็ตาม การสร้างสถานการณ์การทำงานที่สมจริงและเป็นตัวแทน ซึ่งครอบคลุมโหมดกำลังไฟฟ้าทั้งหมดที่เป็นไปได้ในการใช้งานจริงในทุกโหมดนั้นไม่ใช่เรื่องง่าย ข้อผิดพลาดที่พบบ่อยคือการใช้เวกเตอร์การทำงานเพื่อยืนยันฟังก์ชันการทำงานในการคำนวณกำลังไฟฟ้า เวกเตอร์เหล่านี้อาจทำให้เข้าใจผิดและไม่เกี่ยวข้องกับการวิเคราะห์กำลังไฟฟ้า เวกเตอร์การทำงานที่ดีสามารถสร้างได้ด้วยตนเอง โดยอัตโนมัติด้วยเครื่องมือไฟฟ้า ("แบบไร้เวกเตอร์") หรือด้วยโปรแกรมจำลองฮาร์ดแวร์ที่รันแอปพลิเคชันจริง

ผลิตภัณฑ์

December 20, 2025

การออกแบบ IC พลังงานต่ำ: เทคนิคและแนวทางปฏิบัติที่ดีที่สุด

บทความนี้จะสรุปเทคนิคการออกแบบที่จำเป็นและแนวทางปฏิบัติที่ดีที่สุดสำหรับการใช้งานอย่างมีประสิทธิผล

by

นักเขียนบทความ