ผลิตภัณฑ์

19

Jan

การประยุกต์ใช้ AI/ML กับการออกแบบวงจรสัญญาณแบบอะนาล็อกและแบบผสม

สํารวจว่าอัลกอริทึมอัจฉริยะกําหนดความแม่นยําใหม่ในระบบแอนะล็อกและสัญญาณผสมได้อย่างไร

การออกแบบวงจรอนาล็อก สัญญาณผสม และ RF เป็นกระบวนการแบบแมนนวลทั้งหมด กระบวนการทางวิศวกรรมอาศัยการพัฒนา "ความรู้สึก" สําหรับสิ่งต่าง ๆ โดยทําซ้ําแล้วซ้ําเล่า โดยการเรียนรู้ว่าอะไรได้ผลและอะไรไม่ได้ผล สัญชาตญาณเป็นสกุลเงินที่เราสร้างอาชีพวิศวกรรมและภาคภูมิใจที่คิดว่ามันไม่สามารถถูกแทนที่ได้ แต่มันคืออะไร?

ยุคของ AI มาถึงเราแล้ว อินเทอร์เน็ตเต็มไปด้วยผู้คนและธุรกิจที่พยายามควบคุมพลังของ AI เพื่อนําเราเข้าสู่ยุคเทคโนโลยีใหม่ แต่เราสามารถสอนเครื่องจักรให้มีสัญชาตญาณที่เราทําได้มากน้อยเพียงใด?

ในบทความนี้ เราจะเรียนรู้เกี่ยวกับเฟรมเวิร์กที่ใช้แมชชีนเลิร์นนิงสี่แบบที่แก้ไขปัญหาของการสร้างการออกแบบแอนะล็อกอัตโนมัติ:

- Berkeley Analog Generator: เครื่องมือออกแบบแบบ end-to-end ที่สร้างแผนผัง เค้าโครง และแยกปรสิตโดยอัตโนมัติ

- AutoCkt: เฟรมเวิร์กที่ใช้การเรียนรู้แบบเสริมแรงที่ใช้การจําลองน้อยกว่า 10 เท่าเพื่อให้ได้โซลูชันการออกแบบที่เหมาะสมที่สุดเมื่อเทียบกับที่ล้ําสมัยในปัจจุบัน

- ALIGN: เครื่องมือสร้างเลย์เอาต์อัตโนมัติที่สร้างขึ้นด้วยลําดับชั้น

- มหัศจรรย์: ตัวสร้างเลย์เอาต์ตามลําดับชั้นที่คํานึงถึงข้อกําหนดความสมมาตรของเค้าโครง

มาดําน้ํากันเถอะ! อย่าลังเลที่จะข้ามไปยังประเด็นสําคัญในตอนท้ายหากคุณมีเวลาน้อย

การสร้างการออกแบบอัตโนมัติ

นอกเหนือจากการแข่งขันเพื่อใช้ซิลิกอนสําหรับ AI ที่ใช้หม้อแปลงแล้วความตื่นเต้นสําหรับงานวิศวกรรมยังมาจากลักษณะการสร้างของ AI โอกาสที่จะ "ขอให้" AI ออกแบบวงจรอิเล็กทรอนิกส์และให้มันสร้างการออกแบบที่ทํางานได้อย่างเต็มที่ซึ่งได้รับการปรับให้เหมาะสมกว่าที่มนุษย์สามารถทําได้นั้นน่าสนใจอย่างปฏิเสธไม่ได้ ความสามารถในการสร้างภาพโดยใช้เครื่องมือต่างๆ เช่น DALL-E, Midjourney และ Stable Diffusion และวิดีโอโดยใช้ Sora ทําให้เราจินตนาการว่าเราสามารถสร้างเค้าโครงชิปได้ด้วยวิธีเดียวกัน ด้วยทรัพยากรที่เพียงพอความพยายามของมนุษย์ที่มีแนวโน้มที่จะเกิดข้อผิดพลาดหลายปีจะถูกแทนที่ด้วยการออกแบบเครื่องจักรที่ทําซ้ําได้หลายชั่วโมง นั่นคือความฝันในยูโทเปียอยู่แล้ว

สําหรับงานวิศวกรรมอัลกอริธึมการเพิ่มประสิทธิภาพเทคนิคการเรียนรู้ของเครื่องและโครงข่ายประสาทเทียมเป็นขนมปังและเนยสําหรับการออกแบบอัตโนมัติที่ชาญฉลาด การถือกําเนิดของโมเดลภาษาขนาดใหญ่ได้กระตุ้นความสนใจใหม่ในพื้นที่เหล่านี้ภายใต้ชื่อเล่นของ AI แต่แม้ในยุคก่อนหม้อแปลงของ AI นักวิจัยก็มุ่งเน้นไปที่การใช้แมชชีนเลิร์นนิงเพื่อแก้ปัญหาเร่งด่วนอย่างหนึ่งในการออกแบบแอนะล็อก: การสร้างการออกแบบอัตโนมัติ

ปัญหาของการออกแบบอนาล็อก

แม้ว่าเค้าโครงดิจิทัลในปัจจุบันจะทําโดยใช้สถานที่และเส้นทาง แต่เค้าโครงสัญญาณแบบอะนาล็อกและสัญญาณผสมจะทําด้วยตนเองโดยวิศวกรที่มีทักษะสูงทําให้เป็นกระบวนการที่ใช้เวลานาน ความซับซ้อนในการออกแบบที่เกี่ยวข้องนั้นสูงกว่ามากเพื่อให้แน่ใจว่ามีความสมมาตรของเลย์เอาต์ลดการสูญเสียและการกระจายตัวและคํานึงถึงเอฟเฟกต์การมีเพศสัมพันธ์และปรสิต

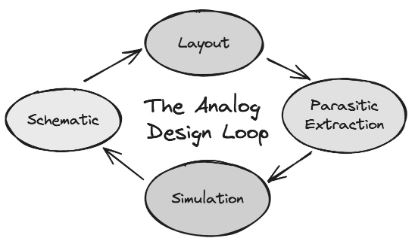

ปรสิตเค้าโครงกําหนดว่าค่าแผนผังจําเป็นต้องออกแบบใหม่เมื่อนํามาพิจารณาแล้ว ลูปวนซ้ําของการออกแบบแผนผังการสร้างเค้าโครงการสกัดปรสิตและการประเมินประสิทธิภาพถือเป็นส่วนสําคัญที่ใช้เวลานานของกระบวนการออกแบบ

ความพยายามในอดีตในการสร้างเลย์เอาต์แบบอะนาล็อกโดยอัตโนมัติไม่ได้ติดอยู่ในอุตสาหกรรมเสมอไป ยักษ์ใหญ่ของ EDA เช่น Cadence Design Systems และ Synopsys ได้จัดเตรียมเครื่องมือสําหรับการสร้างเค้าโครงอัตโนมัติจากแผนผัง อย่างไรก็ตามผลลัพธ์ไม่ได้ดึงดูด "สุนทรียศาสตร์" ของนักออกแบบวงจรที่มีประสบการณ์เสมอไป เป็นความเชื่อพื้นฐาน (และอาจถูกต้อง) ว่าการออกแบบที่สวยงามนั้นแข็งแกร่งต่อเอฟเฟกต์เลย์เอาต์ซึ่งมักไม่ค่อยได้รับการจําลองอย่างแม่นยํา

มีสาเหตุหลายประการที่ทําให้เลย์เอาต์อนาล็อกอัตโนมัติมีความเกี่ยวข้องมากขึ้นในปัจจุบันมากกว่าที่เคยเป็นมา:

- โหนดเทคโนโลยีสมัยใหม่มีกฎการออกแบบที่เข้มงวดสูงซึ่ง:

- ทําให้ยากต่อการสร้างการออกแบบด้วยตนเอง

- ลดพื้นที่การออกแบบโดยรวมที่จะสํารวจสําหรับการสร้างเลย์เอาต์

- ความต้องการเนื้อหาแบบอะนาล็อกเพิ่มขึ้นนักออกแบบที่มีประสบการณ์ขาดแคลนรอบเวลาการออกแบบลดลงในขณะที่ข้อมูลจําเพาะมีความท้าทายมากขึ้น

- การเคลื่อนย้ายการออกแบบระหว่างโหนดเทคโนโลยีเป็นสิ่งสําคัญสําหรับเหตุผลด้านเทคโนโลยีและธุรกิจที่หลากหลาย เราต้องการวิธีแปลการออกแบบอย่างรวดเร็ว

- การถือกําเนิดของเทคนิคการเรียนรู้ของเครื่องและตอนนี้ AI ที่ใช้หม้อแปลงมอบโอกาสใหม่ในการแก้ปัญหาการออกแบบแอนะล็อกอัตโนมัติ

โดยพื้นฐานแล้ว เราต้องการเครื่องมือในการแปลข้อกําหนดการออกแบบเป็นแผนผังและเค้าโครงที่ตรงตามข้อกําหนดและสามารถผลิตได้โดยมีการแทรกแซงของมนุษย์น้อยที่สุด เราจะดูกรอบการทํางานดังกล่าวบางส่วนที่เปิดใช้งานสิ่งนี้ในวันนี้

าเนิดไฟฟ้าอนาล็อกเบิร์กลีย์ (BAG)

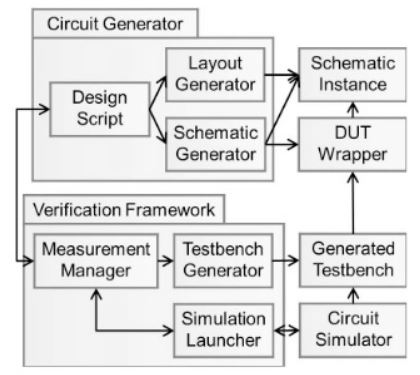

Berkeley Analog Generator (BAG) เป็นเฟรมเวิร์กที่ใช้ python สําหรับการสร้างวงจรสัญญาณอะนาล็อกและสัญญาณผสม มันเป็นมากกว่าเครื่องมือเพิ่มประสิทธิภาพธรรมดา ด้วยเน็ตลิสต์เทมเพลตวงจรและข้อมูลจําเพาะเป้าหมายเป็นอินพุตจะทําการจําลองการรับรู้ปรสิตซ้ําๆ เพื่อมาบรรจบกันในแผนผังและเลย์เอาต์ที่ใช้งานได้

โฟลว์การออกแบบโดยละเอียดมีลักษณะดังนี้:

- เทมเพลตแผนผัง: นักออกแบบสร้างแผนผังวงจรที่เหมาะสมกับการออกแบบ BAG จะสร้างการออกแบบโดยการคัดลอกและแก้ไขเทมเพลตนี้

- พารามิเตอร์: นักออกแบบเลือกพารามิเตอร์ในการออกแบบเช่นขนาดทรานซิสเตอร์เป็นตัวแปรที่ต้องกําหนด

- เครื่องกําเนิดไฟฟ้า: นักออกแบบเขียนตัวสร้างแผนผังโดยใช้ BAG python API ตัวสร้างแผนผังจะแปลงเทมเพลตเป็นอินสแตนซ์วงจรที่มีการรวมพารามิเตอร์ต่างๆ ได้ทันที นักออกแบบยังเขียนตัวสร้างเลย์เอาต์โดยใช้เอ็นจิ้นเลย์เอาต์ที่ไม่ขึ้นกับกระบวนการสองตัวที่จัดทําโดย BA ที่เรียกว่า Xbase และ Laygo สิ่งนี้ทําให้เกิดเลย์เอาต์ที่สะอาดของ DRC/LVS และการสกัดปรสิต

- สคริปต์การออกแบบ: นักออกแบบเขียนสคริปต์เพื่อออกแบบวงจร มันเกี่ยวข้องกับขั้นตอนต่อไปนี้:

- รับจุดเริ่มต้นการคาดเดาที่ดีสําหรับพารามิเตอร์การออกแบบ

- ระบุพารามิเตอร์การวัดของวงจร (เช่น เกนและแบนด์วิดท์)

- ประเมินผลลัพธ์ของตัวสร้างแผนผังและเค้าโครง BAG จะตั้งค่า testbench ทําการจําลอง และคํานวณประสิทธิภาพของวงจรโดยอัตโนมัติด้วยเน็ตลิสต์ที่แยกออกมา

- เปรียบเทียบข้อมูลจําเพาะของวงจรกับผลการจําลอง และสร้างชุดพารามิเตอร์ใหม่สําหรับเครื่องกําเนิดไฟฟ้า

- ทําซ้ําโดยอัตโนมัติจนกว่าจะได้ผลลัพธ์ที่ต้องการ

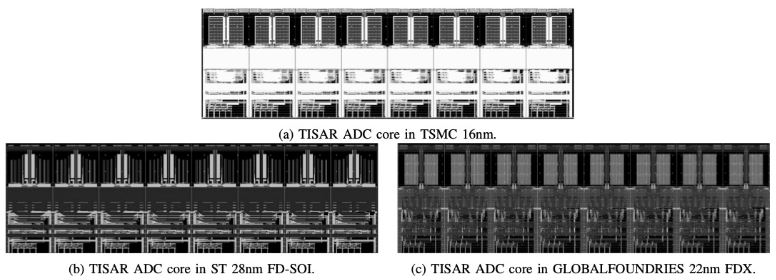

นักวิจัยได้สร้างการออกแบบเต็มรูปแบบของตัวแปลงอนาล็อกเป็นดิจิตอลโดยประมาณต่อเนื่องแบบสอดแทรกเวลา (SAR ADC) และส่วนหน้าของตัวรับส่งสัญญาณ SerDes ในกระบวนการ TSMC 16nm ซึ่งจากนั้นพวกเขาจึงดําเนินการจําลองไปยังโหนดกระบวนการอื่น ๆ จากทั้ง TSMC และ GlobalFoundries ได้อย่างง่ายดาย อ่านเอกสารต้นฉบับหากคุณสนใจรายละเอียดเพิ่มเติม

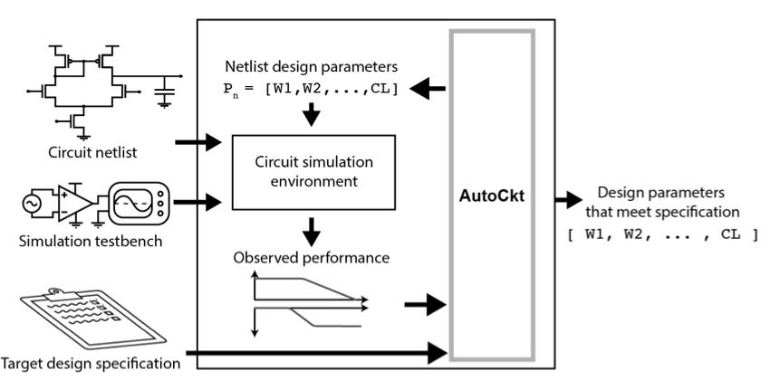

ออโต้

AutoCkt ยกระดับ BAG ไปอีกขั้น ปัญหาของ BAG คือต้องการจุดออกแบบเบื้องต้น จากนั้นจึงหาวิธีแก้ปัญหาที่เหมาะสมที่สุดซ้ําๆ สิ่งนี้นําเสนอความท้าทายสองประการ:

- วิธีการเพิ่มประสิทธิภาพที่สุ่มตัวอย่างพื้นที่เริ่มต้นไม่ได้มาบรรจบกันเสมอไป

- หากข้อกําหนดการออกแบบมีการเปลี่ยนแปลง การเพิ่มประสิทธิภาพจะต้องเริ่มต้นใหม่ตั้งแต่ต้น

สิ่งที่เราต้องการคือเข้าหาปัญหาเหมือนนักออกแบบที่เป็นมนุษย์ ด้วยการทําความเข้าใจพื้นที่การออกแบบที่มีอยู่โดยสัญชาตญาณเราต้องการอัลกอริทึมเพื่อเรียนรู้การแลกเปลี่ยนระหว่างข้อกําหนดเป้าหมายที่แตกต่างกันในพื้นที่การออกแบบ

AutoCkt ทําเช่นนี้ด้วยตัวแทนการเรียนรู้แบบเสริมกําลัง (RL) ที่ใช้กระบวนการลองผิดลองถูกเหมือนมนุษย์ หากมีพารามิเตอร์หลายตัวที่ต้องปรับให้เหมาะสมในการออกแบบการรวมกันของพารามิเตอร์ทั้งหมดเหล่านี้จะถือเป็นพื้นที่การออกแบบ พารามิเตอร์แต่ละชุดให้ผลลัพธ์จําลอง ซึ่งเปรียบเทียบกับข้อกําหนดที่ต้องการ

กระบวนการเรียนรู้แบบเสริมแรงเกี่ยวข้องกับขั้นตอนต่อไปนี้:

- การสร้างวิถี: เริ่มต้นด้วยพารามิเตอร์เริ่มต้นที่ตั้งไว้ตรงกลางของพื้นที่การออกแบบและทําซ้ําต่อไปจนกว่าผลลัพธ์จําลองจะตรงตามข้อกําหนด การสร้างวิถีหนึ่งได้รับการกล่าวขานว่าสมบูรณ์

- การฝึกอบรมตัวแทน RL: เลือกข้อกําหนดเป้าหมายที่สุ่มเลือกหลายรายการ (เช่น 50) สร้างวิถีสําหรับแต่ละข้อกําหนดเหล่านี้ ขึ้นอยู่กับว่าผลลัพธ์สุดท้ายใกล้เคียงกับข้อกําหนดมากน้อยเพียงใด ให้คะแนนแต่ละวิถี การฝึกอบรมจะสิ้นสุดลงเมื่อตรงตามข้อกําหนดทั้ง 50 ข้อตามคะแนนวิถีเกณฑ์

ตอนนี้หากคุณระบุข้อกําหนดใหม่ที่ไม่ได้อยู่ในการฝึกอบรมตัวแทน RL จะทราบวิถีที่ดีที่สุดที่ใกล้เคียงกับข้อกําหนดที่คุณให้ไว้มากที่สุด หากทราบวิถีแสดงว่าคุณมีจุดเริ่มต้นที่ดีจริงๆสําหรับการออกแบบ ด้วยเหตุนี้ คุณจะต้องทําซ้ําน้อยลงมากเพื่อให้ได้ชุดพารามิเตอร์การออกแบบที่ถูกต้อง

AutoCkt ใช้ BAG เพื่อสร้างข้อมูลการจําลองสําหรับกระบวนการฝึกอบรมทั้งหมด ด้วยเหตุนี้ ปรสิตจากเค้าโครงจึงรวมอยู่ในพื้นที่การฝึกอบรมแล้ว และชุดพารามิเตอร์สุดท้ายจากตัวแทน RL จะให้ค่าที่ใกล้เคียงกับผลลัพธ์สุดท้าย

ผู้เขียนบทความต้นฉบับแสดงให้เห็นว่า AutoCkt ต้องการการทําซ้ําน้อยกว่าวิธีการที่ดีที่สุดในปัจจุบันถึง 10 เท่าซึ่งใช้การผสมผสานระหว่างอัลกอริทึมทางพันธุกรรมและการเรียนรู้ของเครื่อง พวกเขาแสดงให้เห็นว่าพวกเขาสามารถสร้างการออกแบบการส่งผ่าน LVS 40 แบบสําหรับ OTA 2 ขั้นตอนที่มีโหลด gm ติดลบได้ภายในเวลาไม่ถึง 3 วันด้วย CPU แบบ 1 คอร์ มันยอดเยี่ยมมาก

ALIGN และ MAGICAL

จนถึงตอนนี้ เราได้พูดคุยเกี่ยวกับการสร้างเลย์เอาต์โดยไม่ต้องกังวลว่ามีการใช้งานอย่างไร ไม่มีนักออกแบบตัวจริงคนใดต้องการมีเลย์เอาต์ "แบน" โดยไม่มีลําดับชั้นของหน่วยการสร้าง มันไม่ใช่วิธีที่ทําสิ่งต่าง ๆ ในโลกมนุษย์

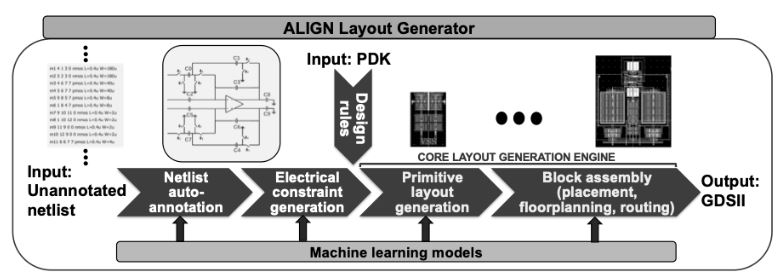

คําตอบแบบเป็นโปรแกรมสําหรับเรื่องนี้คือ ALIGN (Analog Layout, Smartly Generated from Netlists) นี่คือโฟลว์การสร้างเค้าโครงอัตโนมัติแบบโอเพ่นซอร์สสําหรับวงจรแอนะล็อก ซึ่งแปลเน็ตลิสต์อินพุตเป็นเค้าโครง GDSII เอาต์พุต เฉพาะสําหรับเทคโนโลยีที่กําหนด แต่มีคุณสมบัติเพิ่มเติม

ALIGN พยายามสร้างเค้าโครง IC เหมือนกับมนุษย์ สิ่งนี้เกี่ยวข้องกับการระบุลําดับชั้นของเค้าโครง การสร้างเค้าโครงของบล็อคการสร้าง แล้วประกอบในแต่ละระดับของลําดับชั้นเค้าโครง ตัวอย่างเช่น ระดับต่ําสุดของลําดับชั้นจะเป็นทรานซิสเตอร์แต่ละตัว ใช้เพื่อสร้างแบบดั้งเดิม เช่น มิเรอร์ปัจจุบันและคู่ดิฟเฟอเรนเชียล ซึ่งประกอบเป็นโมดูล เช่น แอมพลิฟายเออร์ทรานส์คอนดักแดนซ์ การใช้โมดูลเหล่านี้ระบบเช่นตัวรับส่งสัญญาณ RF จะถูกสร้างขึ้น

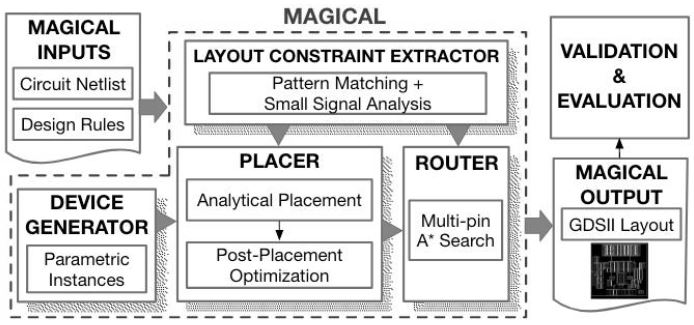

โครงการโอเพ่นซอร์สอีกโครงการหนึ่งที่พยายามสร้างเลย์เอาต์แบบอะนาล็อกอัตโนมัติคือ MAGICAL ซึ่งได้รับการอธิบายว่าเป็น "ระบบเค้าโครง IC แบบอะนาล็อกอัตโนมัติเต็มรูปแบบที่ได้รับแรงบันดาลใจจากสติปัญญาของมนุษย์" ซึ่งได้รับทุนสนับสนุนจาก โปรแกรม DARPA IDEA

การไหลโดยรวมคล้ายกับ ALIGN จากสิ่งที่ฉันสามารถบอกได้ ใช้เน็ตลิสต์อินพุตและสร้างเค้าโครงที่ปรับให้เหมาะสมโดยเน้นที่การสร้างเลย์เอาต์ตามลําดับชั้น ความแตกต่างที่สําคัญมาจากการพิจารณาข้อกําหนดสมมาตรของวงจรที่ MAGICAL ตระหนัก

ตัวอย่างเช่น MAGICAL ให้ความสําคัญกับการทําให้แน่ใจว่าทรานซิสเตอร์ดิฟเฟอเรนเชียลตรงกันโดยการระบุแหล่งที่มาของทรานซิสเตอร์ที่เชื่อมต่อกันเพื่อสร้างกราวด์เสมือนโดยอิงจากกระบวนการที่เรียกว่า "การตรวจจับรูปแบบเมล็ดพันธุ์" นอกจากนี้ยังวางองค์ประกอบแบบพาสซีฟที่จับคู่อย่างเหมาะสม ในขั้นตอนสุดท้าย เลย์เอาต์จะถูกประมวลผลภายหลังเพื่อระบุแหล่งที่มาของสมมาตรเพิ่มเติมที่อาจพลาดไปในความพยายามครั้งแรก เช่น สมมาตรของวงจรอคติโดยมองหาทรานซิสเตอร์ที่เชื่อมต่อเกตหรือไดโอดทั่วไป

สิ่งพิมพ์ที่ใช้เครื่องมือทั้งสองนี้แสดงให้เห็นว่าพวกเขาสามารถสร้างการออกแบบที่ตรงกับประสิทธิภาพการทํางานกับวงจรที่ออกแบบโดยมนุษย์

ปิดท้าย

เมื่อเร็ว ๆ นี้ บริษัทสตาร์ทอัพชื่อ Astrus กําลังมองหาการสร้างเลย์เอาต์แบบอะนาล็อกในเชิงพาณิชย์จากโตรอนโต ประเทศแคนาดา พวกเขาร่วมก่อตั้งโดย Brad Moon และ Zeyi Wang เมื่อเร็ว ๆ นี้ได้ประกาศรอบการระดมทุนล่วงหน้ามูลค่า 2.4 ล้านดอลลาร์ Moon กล่าวว่าการสร้างเลย์เอาต์แบบอะนาล็อกนําเสนอปัญหาที่เฉพาะเจาะจงและมีมูลค่าสูงสําหรับนักออกแบบอนาล็อก 60,000 คนทั่วโลก ด้วยความต้องการชิปที่เพิ่มขึ้นและการขาดแคลนวิศวกรอะนาล็อกที่มีทักษะสูง Astrus จึงมีโอกาสหลายล้านดอลลาร์ในมือ

ความก้าวหน้าเหล่านี้น่าตื่นเต้น แต่การออกแบบด้วยเครื่องจักรจะไม่แทนที่วิศวกรออกแบบสัญญาณอะนาล็อกและสัญญาณผสมโดยสิ้นเชิง สิ่งที่จะเปลี่ยนไปคือวิธีที่เราจะดําเนินการในฐานะนักออกแบบ แทนที่จะวางส่วนประกอบวงจรด้วยตนเองและวาดสายไฟบนเครื่องมือแผนผังความฉลาดของเครื่องจักรจะช่วยให้เรากําจัดชิ้นส่วนที่น่าเบื่อโดยอัตโนมัติเพื่อให้เราสามารถมุ่งเน้นไปที่แนวคิดวงจรที่ยอดเยี่ยมแทน

ผลิตภัณฑ์

February 6, 2026

การประยุกต์ใช้ AI/ML กับการออกแบบวงจรสัญญาณแบบอะนาล็อกและแบบผสม

สํารวจว่าอัลกอริทึมอัจฉริยะกําหนดความแม่นยําใหม่ในระบบแอนะล็อกและสัญญาณผสมได้อย่างไร

by

นักเขียนบทความ