ผลิตภัณฑ์

19

Jan

การออกแบบการข้ามโดเมนนาฬิกาและ FIFO

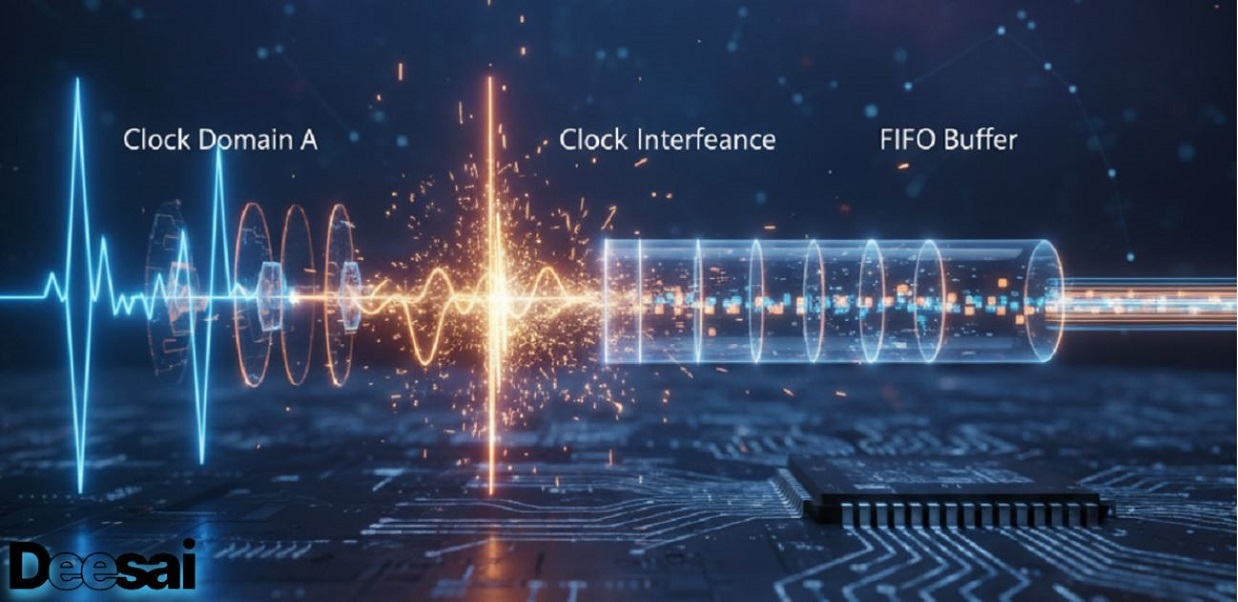

บทความนี้จะเจาะลึกถึงการข้ามโดเมนนาฬิกา (CDC) และการออกแบบ FIFO ที่ให้โซลูชันที่เชื่อถือได้อย่างไร

ในระบบดิจิทัล การจัดการกับโดเมนนาฬิกาหลายโดเมนมักหลีกเลี่ยงไม่ได้

เมื่อข้อมูลจำเป็นต้องเคลื่อนย้ายระหว่างส่วนประกอบที่ทำงานด้วยความเร็วสัญญาณนาฬิกาที่ต่างกัน การรับรองการถ่ายโอนข้อมูลที่แม่นยำกลายเป็นเรื่องยาก

นี่คือจุดที่เทคนิค Clock Domain Crossing (CDC) และบัฟเฟอร์ FIFO เข้ามามีบทบาท

ในบทความนี้ เราจะเรียนรู้ว่า CDC ทำงานอย่างไร ปัญหาที่เกิดขึ้นเมื่อจัดการโดเมนนาฬิกาหลายโดเมน และการออกแบบ FIFO จะให้โซลูชันที่เชื่อถือได้อย่างไร

ทำความเข้าใจเกี่ยวกับการข้ามโดเมนนาฬิกา (CDC)

สัญญาณรบกวนโดเมนนาฬิกา (CDC) คือกระบวนการถ่ายโอนสัญญาณจากโดเมนนาฬิกาหนึ่งไปยังอีกโดเมนนาฬิกาหนึ่ง ซึ่งสัญญาณนาฬิกาไม่ซิงค์กัน หมายความว่าสัญญาณนาฬิกาแต่ละโดเมนมีความแตกต่างกันในด้านความถี่ เฟส หรือทั้งสองอย่าง หาก CDC ไม่ได้รับการจัดการอย่างเหมาะสม สัญญาณอะซิงโครนัสอาจนำไปสู่ปัญหาต่างๆ เช่น ความไม่เสถียร การสูญเสียข้อมูล หรือความไม่สอดคล้องกัน ซึ่งทั้งหมดนี้สามารถลดความน่าเชื่อถือของระบบดิจิทัลได้

ปัญหาและแนวทางแก้ไขทั่วไปของ CDC

1. ความไม่เสถียร:

- ในขณะที่ข้อมูลไหลจากโดเมนนาฬิกาหนึ่งไปยังอีกโดเมนหนึ่ง สัญญาณอาจไม่เสถียรที่ขอบสัญญาณนาฬิกาตัวรับ ส่งผลให้เกิดความไม่เสถียร

- วิธีแก้ปัญหา: ใช้ซิงโครไนเซอร์แบบฟลิปฟล็อปสองตัว วิธีการนี้จะส่งสัญญาณข้ามโดเมนผ่านฟลิปฟล็อปสองตัวในโดเมนสัญญาณนาฬิกาของผู้รับ ซึ่งจะช่วยลดความเป็นไปได้ของการเกิดไฮเปอร์สเตบิไลเซอร์

2. การสูญเสียข้อมูล:

- หากสัญญาณต้นทางเปลี่ยนแปลงเร็วเกินไป สัญญาณนาฬิกาที่รับอาจพลาดการเปลี่ยนแปลงภายในรอบข้อมูลเดียวกัน ส่งผลให้ข้อมูลสูญหาย

- โซลูชัน: ใช้โปรโตคอลการจับมือหรือบัฟเฟอร์ FIFO เพื่อให้แน่ใจว่ามีการถ่ายโอนข้อมูลที่สมบูรณ์และเชื่อถือได้ข้ามโดเมนนาฬิกา

3. ความไม่สอดคล้องของข้อมูล:

- เมื่อมีการถ่ายโอนข้อมูลหลายบิตระหว่างโดเมนนาฬิกา การจับเวลาของนาฬิกาที่ไม่ตรงกันอาจทำให้เกิดการอัปเดตบางส่วน ส่งผลให้ข้อมูลไม่สอดคล้องกัน

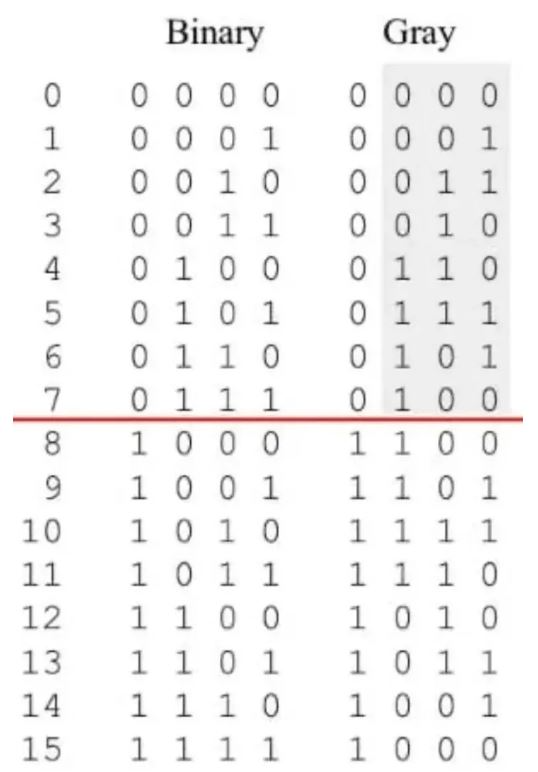

- วิธีแก้ปัญหา: ใช้การเข้ารหัสแบบ Gray หรือบัฟเฟอร์ FIFO ลำดับของรหัส Gray จะเปลี่ยนแปลงเพียงครั้งละหนึ่งบิต ซึ่งช่วยลดความเป็นไปได้ที่ข้อมูลจะไม่สอดคล้องกันระหว่างการส่งข้อมูล

มาเจาะลึกแต่ละวิธีแก้ปัญหาและวิธีแก้ไขปัญหากัน

รองเท้าแตะแบบคู่

ฟลิปฟล็อปแบบซิงโครนัสสองบิตมักใช้สำหรับสัญญาณควบคุมบิตเดียวที่ผ่านโดเมนนาฬิกา เช่น สัญญาณเปิดใช้งาน สัญญาณรีเซ็ต หรือแฟล็กสถานะ

สำหรับสัญญาณข้อมูลหลายบิต ไม่ควรใช้ซิงโครไนเซอร์ฟลิปฟล็อปสองตัว เนื่องจากจะซิงโครไนซ์เฉพาะเวลาสัญญาณเท่านั้น ไม่ใช่ข้อมูล

สำหรับข้อมูลหลายบิต จะใช้บัฟเฟอร์ FIFO หรือเทคนิค CDC เฉพาะทางอื่นๆ

บัฟเฟอร์ FIFO

ในการออกแบบ FIFO (First-In-First-Out) มีเป้าหมายหลักสามประการ:

1. การจัดการอัตราข้อมูลที่แตกต่างกัน:

หากสร้างข้อมูลด้วยอัตราที่เร็วกว่าการใช้มาก อาจมีความเสี่ยงที่จะสูญเสียข้อความได้

โดยการใช้หน่วยความจำ FIFO ผู้ส่งที่รวดเร็วสามารถเขียนข้อมูลตามที่ต้องการและผู้รับที่ช้ากว่าสามารถดึงข้อมูลตามความเร็วของตนเองได้โดยไม่สูญหาย

2. ใช้ Gray Code เพื่อทำให้โดเมนครอสคล็อกมีเสถียรภาพ:

ในสถานการณ์ที่เกี่ยวข้องกับการรบกวนโดเมนนาฬิกา เมื่อมีการส่งข้อมูลหลายบิตระหว่างโดเมน อาจมีความเสี่ยงที่จะเกิดความไม่สอดคล้องกันที่ด้านผู้รับ

ความไม่สอดคล้องกันนี้เกิดขึ้นเมื่อบิตบางส่วนสะท้อนค่าใหม่ในขณะที่บิตอื่นๆ ยังคงค่าเดิมไว้

การนำ Gray Code มาใช้กับตัวชี้ โดยจะมีการเปลี่ยนแปลงครั้งละหนึ่งบิตเท่านั้น จะช่วยลดความเสี่ยงของการเสียหายของบิตและข้อมูลที่ไม่สอดคล้องกัน

ดังนั้นจึงมักใช้ Gray Code เพื่อทำให้การอัปเดตตัวชี้มีเสถียรภาพข้ามโดเมนนาฬิกา ช่วยให้มั่นใจถึงการถ่ายโอนข้อมูลที่ปลอดภัยและเชื่อถือได้ระหว่างการเขียนและการอ่าน

โดยสรุป ตัวชี้ของเราเปลี่ยนแปลงเพียงครั้งละหนึ่งบิตเท่านั้น

วิธีนี้อาจช่วยลดการพลาดได้

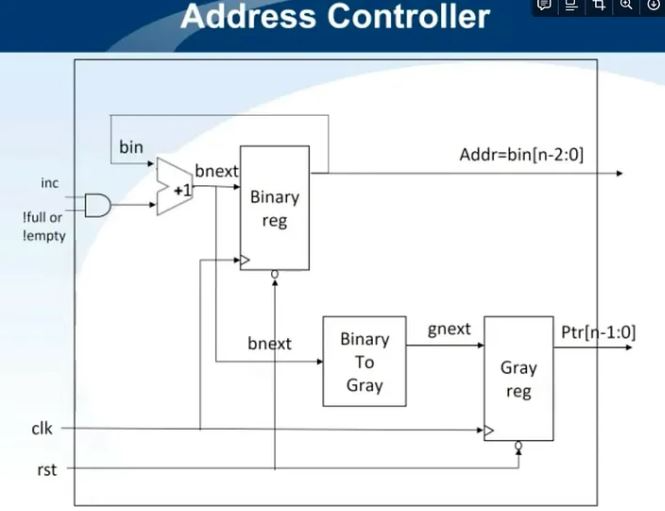

— — เกี่ยวกับตัวควบคุมที่อยู่ใน FIFO — —

การใช้แฟล็กว่าง/เต็มในตรรกะการควบคุม:

ตัวควบคุม FIFO ใช้แฟล็กว่างและแฟล็กเต็มเพื่อกำหนดเวลาที่จะอนุญาตหรือบล็อกการอ่าน/เขียน แฟล็กเหล่านี้ช่วยควบคุมการไหลของข้อมูล ป้องกันการโอเวอร์โฟลว์ (การเขียนไปยัง FIFO เต็ม) หรืออันเดอร์โฟลว์ (การอ่านจาก FIFO ว่าง)

การประยุกต์ใช้ CDC และ FIFO ในการออกแบบที่ซับซ้อน

บัฟเฟอร์ CDC และ FIFO มีความสำคัญในระบบที่มีแหล่งสัญญาณนาฬิกาหลายแหล่ง เช่น โปรเซสเซอร์แบบมัลติคอร์ อินเทอร์เฟซการสื่อสารข้อมูล และระบบสัญญาณผสม การจัดการ CDC อย่างรอบคอบช่วยให้นักออกแบบมั่นใจได้ว่าการทำงานมีเสถียรภาพและเชื่อถือได้ แม้ในการออกแบบที่ซับซ้อนซึ่งระบบย่อยต่างๆ สื่อสารกันแบบอะซิงโครนัส

บทสรุป

บัฟเฟอร์สัญญาณรบกวนโดเมนนาฬิกา (CDC) และ FIFO มีบทบาทสำคัญในการจัดการการถ่ายโอนข้อมูลข้ามโดเมนนาฬิกาแบบอะซิงโครนัสในการออกแบบดิจิทัล

เทคนิค CDC เช่น การซิงโครไนซ์ฟลิปฟล็อปแบบคู่และตัวชี้ Gray Code ช่วยรักษาความสมบูรณ์ของข้อมูลและความเสถียรของเวลา

บัฟเฟอร์ FIFO เป็นวิธีที่มีประสิทธิภาพในการจัดการกับการสูญเสียข้อมูลและรับรองการไหลของข้อมูลอย่างสม่ำเสมอระหว่างโดเมนสัญญาณนาฬิกาที่มีความถี่ต่างกัน

เทคนิคเหล่านี้เมื่อนำมารวมกันจะสร้างรากฐานสำหรับการจัดการข้อมูลอันทรงพลังในระบบมัลติคล็อก

เนื่องจากการออกแบบดิจิทัลยังคงขยายตัวต่อไป การเชี่ยวชาญการออกแบบ CDC และ FIFO จึงมีความจำเป็นสำหรับนักออกแบบทุกคนที่ต้องการสร้างระบบที่เชื่อถือได้และมีประสิทธิภาพสูง

ผลิตภัณฑ์

October 3, 2025

การออกแบบการข้ามโดเมนนาฬิกาและ FIFO

บทความนี้จะเจาะลึกถึงการข้ามโดเมนนาฬิกา (CDC) และการออกแบบ FIFO ที่ให้โซลูชันที่เชื่อถือได้อย่างไร

by

นักเขียนบทความ