ผลิตภัณฑ์

19

Jan

เครื่องสังเคราะห์ความถี่ PLL ดิจิทัล

บทความนี้จะอธิบายว่าเครื่องสังเคราะห์ความถี่ PLL ดิจิทัลใช้ส่วนประกอบดิจิทัลอย่างไรเพื่อสร้างสัญญาณเอาต์พุตที่เสถียรด้วยความถี่ใหม่ที่ต้องการ

.jpg)

เครื่องสังเคราะห์ความถี่ RF แบบดิจิทัล PLL ได้ชื่อมาจากการที่ใช้เทคนิคดิจิทัลในการควบคุมความถี่เอาต์พุต ในบางกรณี เครื่องสังเคราะห์ความถี่ประเภทนี้ถูกเรียกว่าเครื่องสังเคราะห์ดิจิทัลทางอ้อม เนื่องจากสัญญาณเอาต์พุตถูกสร้างขึ้นโดยอ้อมผ่านวงจรล็อกเฟส (PLL) แทนที่จะสร้างขึ้นโดยตรงด้วยการบวก ลบ ฯลฯ

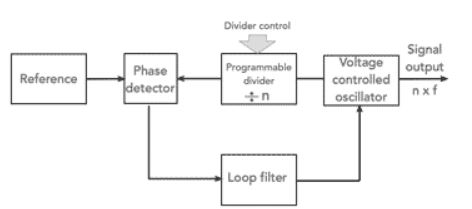

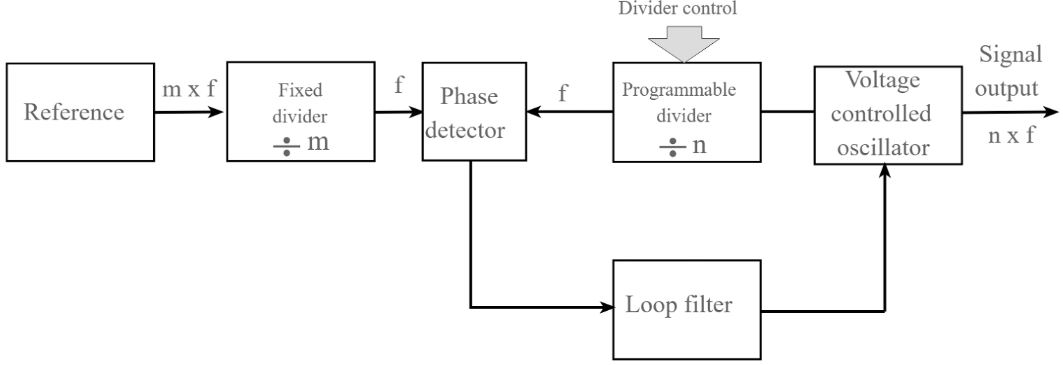

เครื่องสังเคราะห์เสียงแบบ PLL ดิจิทัลใช้ตัวแบ่งดิจิทัลที่อยู่ระหว่าง VCO และตัวตรวจจับเฟส เนื่องจากตัวแบ่งใช้เทคนิคดิจิทัล จึงสามารถเปลี่ยนอัตราส่วนการแบ่งของตัวแบ่งและเปลี่ยนเอาต์พุตจากเครื่องสังเคราะห์เสียงแบบล็อกลูปเฟสได้

เครื่องสังเคราะห์เสียง PLL แบบดิจิทัลมีประโยชน์อย่างยิ่ง เพราะสามารถควบคุมได้ด้วยชุดสายดิจิทัล ซึ่งอาจควบคุมได้จากไมโครโปรเซสเซอร์หรือตัวควบคุม วิธีนี้ช่วยเพิ่มฟังก์ชันการทำงานให้กับระบบต่างๆ ที่ใช้เครื่องสังเคราะห์เสียง PLL แบบดิจิทัลได้อย่างมาก

ปัจจุบันมีชิปสังเคราะห์ RF มากมายหลายรุ่นที่มีรายละเอียดที่ช่วยให้การออกแบบวงจร RF ง่ายที่สุดเท่าที่จะเป็นไปได้ ซึ่งทำให้การออกแบบ RF เป็นเรื่องง่าย และการใช้งานก็น่าสนใจ

พื้นฐานของเครื่องสังเคราะห์เสียงแบบดิจิทัล

เครื่องสังเคราะห์ความถี่ PLL ดิจิทัลใช้เฟสล็อกลูปเป็นพื้นฐานในการทำงาน

เฟสล็อกลูปประกอบด้วยบล็อกวงจรจำนวนหนึ่ง ได้แก่ บล็อกอ้างอิง ตัวตรวจจับเฟส ออสซิลเลเตอร์ควบคุมแรงดันไฟฟ้า และตัวกรอง โดยพื้นฐานแล้ว ลูปจะเปรียบเทียบเฟสของสัญญาณจากวงจรอ้างอิงและ VCO และป้อนเอาต์พุตของตัวตรวจจับเฟสกลับไปยังขั้วควบคุมของ VCO ผ่านตัวกรอง

การรับรู้เอาต์พุตจากตัวตรวจจับเฟสนั้นจะพยายามดึงความถี่ VCO เข้าหาความถี่อ้างอิง ในที่สุดก็ถึงจุดที่แรงดันไฟฟ้าคงที่ถูกจ่ายไปยังขั้วควบคุม VCO ซึ่งหมายความว่ามีความแตกต่างเฟสคงที่ระหว่างสัญญาณอ้างอิงและสัญญาณ VCO เนื่องจากความแตกต่างของเฟสไม่เปลี่ยนแปลง หมายความว่าความถี่ของ VCO และสัญญาณอ้างอิงมีค่าเท่ากันทุกประการ และลูปถูกล็อก

หมายเหตุเกี่ยวกับ Phase Locked Loop (PLL):

เฟสล็อกลูป (PLL) เป็นหน่วยการสร้าง RF ที่มีประโยชน์อย่างมาก PLL ใช้แนวคิดการลดความแตกต่างของเฟสระหว่างสัญญาณสองสัญญาณ ได้แก่ สัญญาณอ้างอิงและออสซิลเลเตอร์ท้องถิ่น เพื่อจำลองความถี่ของสัญญาณอ้างอิง การใช้แนวคิดนี้ทำให้สามารถใช้ PLL ได้หลากหลายรูปแบบ ตั้งแต่เครื่องสังเคราะห์ความถี่ไปจนถึงเครื่องแยกสัญญาณ FM และการสร้างสัญญาณใหม่

ในการพัฒนาเฟสล็อกลูปให้เป็นเครื่องสังเคราะห์ความถี่ PLL แบบดิจิทัล จะต้องมีการวางตัวแบ่งแบบดิจิทัลระหว่าง VCO และตัวตรวจจับเฟสเพื่อแบ่งความถี่ VCO ลง

วิธีการเพิ่มตัวแบ่งดิจิทัลให้กับลูปเครื่องสังเคราะห์ความถี่สามารถดูได้จากแผนภาพด้านล่าง

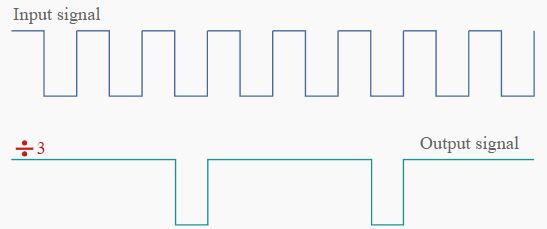

ตัวแบ่งหรือตัวนับแบบตั้งโปรแกรมได้ถูกนำมาใช้ในหลากหลายสาขาของอิเล็กทรอนิกส์ รวมถึงการประยุกต์ใช้คลื่นความถี่วิทยุมากมาย ตัวแบ่งจะรับพัลส์เทรนดังที่แสดงด้านล่าง และให้สัญญาณเทรนที่ช้ากว่า

ในวงจรหารด้วยสอง จะมีพัลส์ออกมาเพียงหนึ่งพัลส์ต่อทุกๆ สองพัลส์ที่ป้อนเข้าไป และต่อไปเรื่อยๆ บางพัลส์มีค่าคงที่ โดยมีอัตราส่วนการแบ่งเพียงค่าเดียว บางพัลส์สามารถตั้งโปรแกรมได้ และป้อนข้อมูลดิจิทัลหรือลอจิกเข้าไปเพื่อกำหนดอัตราส่วนการแบ่งได้

เมื่อเพิ่มตัวแบ่งเข้าไปในวงจร วงจรล็อกเฟส (PLL) จะยังคงพยายามลดความต่างเฟสระหว่างสัญญาณทั้งสองที่เข้าสู่ตัว เปรียบเทียบเฟสเมื่อวงจรอยู่ในสถานะล็อก สัญญาณทั้งสองที่เข้าสู่ตัวเปรียบเทียบจะมีความถี่เท่ากันทุกประการ เพื่อให้เป็นจริง ออสซิลเลเตอร์ที่ควบคุมด้วยแรงดันไฟฟ้าจะต้องทำงานที่ความถี่เท่ากับความถี่การเปรียบเทียบเฟสคูณอัตราส่วนการแบ่ง

จะเห็นได้ว่าหากอัตราส่วนการแบ่งถูกเปลี่ยนแปลงไปหนึ่ง ออสซิลเลเตอร์ที่ควบคุมด้วยแรงดันไฟฟ้าจะต้องเปลี่ยนไปเป็นทวีคูณถัดไปของความถี่อ้างอิง ซึ่งหมายความว่าความถี่ขั้นบันไดของเครื่องสังเคราะห์เสียงจะเท่ากับความถี่ที่เข้าสู่ตัวเปรียบเทียบ

การเพิ่มขั้นความถี่

จากการทำงานของเครื่องสังเคราะห์ความถี่ดิจิทัลพื้นฐาน จะเห็นได้ว่าความถี่เอาต์พุตมีค่าเท่ากับ 'n' คูณความถี่การเปรียบเทียบเฟส โดยที่ 'n' คืออัตราส่วนการแบ่ง การเปลี่ยนอัตราส่วนการแบ่งหนึ่งคือการเปลี่ยนแปลงความถี่ที่น้อยที่สุดที่สามารถทำได้

จากผลการทดลองจะเห็นได้ว่าการเปลี่ยนแปลงความถี่ที่น้อยที่สุดที่สามารถทำได้จะเท่ากับความถี่เปรียบเทียบ นั่นคือ ความถี่ตัวตรวจจับเฟส ในรูปแบบพื้นฐานของเครื่องสังเคราะห์ความถี่ดิจิทัล ความถี่นี้จะเท่ากับความถี่อ้างอิง

เครื่องสังเคราะห์เสียงส่วนใหญ่จำเป็นต้องสามารถปรับความถี่เป็นขั้นบันไดเสียงที่เล็กลงได้มากหากต้องการให้ใช้งานได้ บ่อยครั้งที่จำเป็นต้องใช้ความถี่ขั้นบันไดเสียงขนาด 10 kHz, 12.5 kHz หรือ 25 kHz ในกรณีที่วิทยุทำงานภายในช่องสัญญาณที่กำหนดต่างกัน และสำหรับวิทยุที่ต้องปรับจูนอย่างต่อเนื่อง อาจจำเป็นต้องใช้ความถี่ขั้นบันไดเสียงขนาด 100 Hz หรือน้อยกว่า

เพื่อให้บรรลุสิ่งนี้ จำเป็นต้องลดความถี่ในการเปรียบเทียบ ซึ่งโดยทั่วไปทำได้โดยการใช้ออสซิลเลเตอร์อ้างอิงที่ความถี่ประมาณหนึ่งเมกะเฮิรตซ์ แล้วแบ่งสัญญาณนี้ลงไปยังความถี่ที่ต้องการโดยใช้ตัวแบ่งคงที่ วิธีนี้จะทำให้ได้ความถี่ในการเปรียบเทียบที่ต่ำ

โดยทั่วไปแล้ว ออสซิลเลเตอร์อ้างอิงจะทำงานที่ความถี่ไม่กี่ MHz โดยมักจะเป็น 5 MHz หรือ 10 MHz เนื่องจากที่ความถี่เหล่านี้ ประสิทธิภาพจะดีกว่าและสามารถผลิตคริสตัลได้ในขนาดที่ต้องการ

การใช้ตัวแบ่งความถี่หลังเครื่องกำเนิดสัญญาณอ้างอิงช่วยให้สามารถเปรียบเทียบความถี่เฟสต่ำได้ ขณะเดียวกันก็ให้ออสซิลเลเตอร์อ้างอิงทำงานที่ความถี่ที่สะดวก ซึ่งมักจะอยู่ที่ประมาณ 10 MHz

เมื่อพัฒนาเครื่องสังเคราะห์เสียงดิจิทัลที่มีความถี่อ้างอิงต่ำ หมายความว่าตัวแบ่งแบบตั้งโปรแกรมได้จะมีอัตราส่วนการแบ่งที่สูงกว่ามาก เนื่องจากจำเป็นต้องแบ่งลงจากความถี่เอาต์พุตไปยังความถี่เปรียบเทียบที่ต่ำกว่า ซึ่งอาจนำไปสู่ปัญหาความล่าช้าผ่านตัวแบ่ง รวมถึงปัญหาสัญญาณรบกวนเฟสสูงและอื่นๆ

ความแม่นยำและเสถียรภาพของความถี่ PLL ดิจิทัล

ปัญหาหนึ่งของออสซิลเลเตอร์ เช่น ออสซิลเลเตอร์ความถี่แปรผันแบบอิสระ (free running) คือ ออสซิลเลเตอร์เหล่านี้ไม่เสถียรนักและปรับเทียบได้ยาก เนื่องจากเป็นวงจรอนาล็อก จึงมีแนวโน้มที่จะเกิดการดริฟต์ และอาจต้องใช้เครื่องปรับเทียบเพิ่มเติมเพื่อให้แน่ใจว่าความถี่ถูกต้อง อันที่จริง วิทยุสื่อสารรุ่นเก่าที่ใช้ออสซิลเลเตอร์ความถี่แปรผันแบบอิสระที่จูนด้วย LC ในการออกแบบ RF มักจะติดตั้งเครื่องปรับเทียบคริสตัลเพื่อตรวจสอบการปรับเทียบความถี่

โชคดีที่การใช้เครื่องสังเคราะห์ความถี่ PLL แบบดิจิทัล ความถี่จะถูกกำหนดโดยคริสตัลออสซิลเลเตอร์ ซึ่งหมายความว่าประสิทธิภาพของคริสตัลออสซิลเลเตอร์จะเป็นตัวกำหนดเสถียรภาพความถี่ของเครื่องสังเคราะห์ทั้งหมด

ในความเป็นจริง ความเสถียรของความถี่ในแง่ของการดริฟต์ความถี่ในส่วนต่อล้านนั้นจะเป็นไปตามเอาต์พุตสุดท้าย

เห็นได้ชัดว่าเสถียรภาพความถี่สัมบูรณ์ในแง่ของดริฟต์ในหน่วยเฮิรตซ์/°C จะถูกคูณด้วยอัตราส่วนการคูณทั้งหมดของลูป กล่าวอีกนัยหนึ่ง หากออสซิลเลเตอร์อ้างอิงทำงานที่ 10 เมกะเฮิรตซ์ และเอาต์พุตสุดท้ายอยู่ที่ 150 เมกะเฮิรตซ์ และตัวเลขสัมบูรณ์ใดๆ ของดริฟต์จะถูกคูณด้วย 150/10 = 15 อย่างไรก็ตาม ในแง่ของดริฟต์ในหน่วยส่วนต่อล้านส่วน ตัวเลขนี้จะยังคงเท่าเดิม เนื่องจากตัวเลขนี้เป็นอัตราส่วน

ตัวอย่างของเครื่องสังเคราะห์ความถี่ PLL แบบดิจิทัล

การให้ตัวเลขจริงมักจะช่วยได้มากในการทำความเข้าใจการทำงานของการออกแบบวงจร RF หรือเทคนิคอื่นๆ

ยกตัวอย่างเช่น ออสซิลเลเตอร์อ้างอิงอาจทำงานที่ความถี่ 1 เมกะเฮิรตซ์ เพื่อให้ได้เสถียรภาพและประสิทธิภาพโดยรวมที่ดีที่สุด จำเป็นต้องใช้ออสซิลเลเตอร์คริสตัล เนื่องจากออสซิลเลเตอร์คริสตัลที่ทำงานในย่านนี้ให้ประสิทธิภาพอ้างอิงที่ดีที่สุด โดยความถี่ 1 เมกะเฮิรตซ์, 5 เมกะเฮิรตซ์ และ 10 เมกะเฮิรตซ์ เป็นความถี่ทั่วไปสำหรับออสซิลเลเตอร์อ้างอิง

สำหรับเครื่องสังเคราะห์เสียงความถี่ 12.5 kHz ซึ่งใช้กันอย่างแพร่หลายสำหรับวิทยุสื่อสารแบบมือถือ FM ย่านความถี่แคบ หรือสถานีฐานสำหรับการสื่อสารทางวิทยุ เพื่อให้ได้ความถี่เปรียบเทียบเฟสที่ 12.5 kHz การออกแบบวงจร RF จำเป็นต้องใช้ตัวแบ่งดิจิทัลที่มีอัตราส่วนการแบ่งคงที่ที่ 80 (1 MHz หารด้วย 80 = 12.5 kHz)

หากเอาต์พุตของเครื่องสังเคราะห์จะทำงานระหว่าง 144 ถึง 146 MHz ตัวแบ่งแบบตั้งโปรแกรมได้จะต้องสามารถให้อัตราส่วนการแบ่งตั้งแต่ 11520 ถึง 11680 ได้

นี่เป็นเพียงตัวอย่างเท่านั้น และสามารถใช้ตัวเลขที่เหมาะสมเพื่อกำหนดช่วงความถี่และขนาดขั้นที่ต้องการได้ ข้อกำหนดหลักคือต้องไม่ทำให้อัตราส่วนการแบ่งสัญญาณมีขนาดใหญ่เกินไปจนทำให้เสถียรภาพของลูปหรือสัญญาณรบกวนเฟสกลายเป็นปัญหา

เครื่องสังเคราะห์เสียง PLL ดิจิทัลและสัญญาณรบกวนเฟส

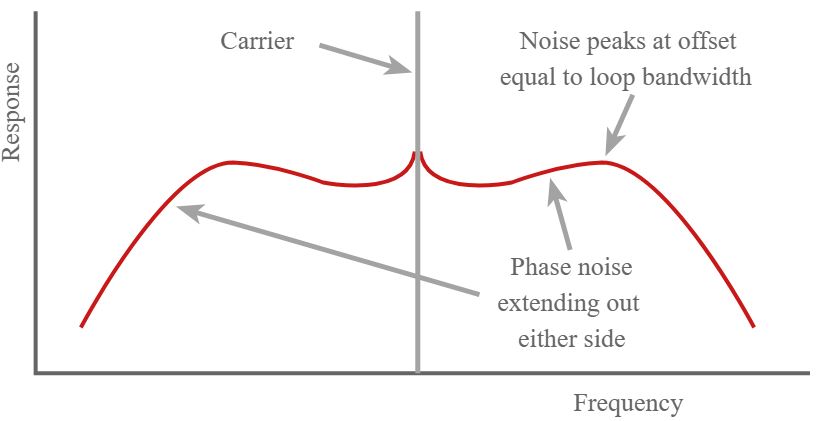

ปัญหาประการหนึ่งของเครื่องสังเคราะห์ความถี่ PLL ดิจิทัลแบบวงจรเดียวก็คือ สัญญาณรบกวนเฟสอาจกลายเป็นปัญหาได้ง่าย

เครื่องรับส่งสัญญาณ VHF / UHF ในยุคแรกๆ หลายเครื่องประสบปัญหาเรื่องสัญญาณรบกวนเฟส ส่งผลให้เครื่องรับมีประสิทธิภาพการทำงานไม่ดี และยังส่งสัญญาณที่มีสัญญาณรบกวนเฟสระดับสูงออกไปทั้งสองด้านของคลื่นพาหะอีกด้วย

สิ่งสำคัญคือต้องแก้ไขปัญหาใดๆ ที่เกี่ยวข้องกับสัญญาณรบกวนเฟสเป็นส่วนหนึ่งของการออกแบบวงจร RF เบื้องต้นสำหรับเครื่องสังเคราะห์เสียง

โชคดีที่สามารถออกแบบวงจรเพื่อลดระดับสัญญาณรบกวนเฟสได้ แม้ว่าการใช้เพียงลูปเดียวก็ทำได้ไม่มากนัก

เครื่องสังเคราะห์ความถี่ PLL แบบดิจิทัลเป็นหนึ่งในเครื่องสังเคราะห์ความถี่ที่ได้รับความนิยมมากที่สุด เทคโนโลยีนี้ได้รับการยอมรับอย่างกว้างขวางและมีไอซีสังเคราะห์ให้เลือกใช้มากมาย ทำให้การออกแบบวงจร RF เป็นเรื่องง่าย นอกจากนี้ เครื่องสังเคราะห์ความถี่ PLL แบบดิจิทัลยังถูกนำไปใช้ในไอซีขนาดใหญ่หลายรุ่นที่ออกแบบมาเพื่อการใช้งานเฉพาะด้าน เช่น บลูทูธ, Wi-Fi และอื่นๆ อีกมากมาย

โดยรวมแล้วเครื่องสังเคราะห์เสียงแบบดิจิทัล PLL ได้ถูกฝังไว้เป็นอย่างดีในวัฒนธรรมการออกแบบวงจร RF และถือเป็นบล็อกการออกแบบวงจรอิเล็กทรอนิกส์ที่ได้รับความนิยมอย่างมาก

ผลิตภัณฑ์

August 21, 2025

เครื่องสังเคราะห์ความถี่ PLL ดิจิทัล

บทความนี้จะอธิบายว่าเครื่องสังเคราะห์ความถี่ PLL ดิจิทัลใช้ส่วนประกอบดิจิทัลอย่างไรเพื่อสร้างสัญญาณเอาต์พุตที่เสถียรด้วยความถี่ใหม่ที่ต้องการ

by

นักเขียนบทความ